# Soft Switched Isolated ZVT Boost DC-DC Converter with Coupled Inductors

R.SAMUEL RAJESH BABU, Research scholar, EEE department, Sathyabama University, Chennai, India. Samuel.rajeshbabu@gmail.com Dr. JOSEPH HENRY, Professor, EEE Department. Vel Tech University, Chennai, India.

Abstract: This paper presents a new Soft switched isolated ZVT boost DC-DC converter with coupled inductors. ZVT realizes soft switching in this converter without imposing additional switching voltage, current stress and conduction loss. primary-parallel-secondary-series employed in this paper to handle the large input current, sustain the high output voltage and extend the voltage gain. The rectifier voltage stress is reduced by the primary-parallel- secondary-series structure. The rectifier reverse-recovery problem is alleviated by the leakage inductance. The above discussed DC-DC converter can be adapted to provide isolation between input and output. Active clamp boost converter with coupled-inductors is proposed for high step-up applications. The detailed design and operating principles are analyzed and described. The simulation results are verified with the experimental results.

*Index Terms*—Active clamp, coupled-inductors, isolated boost converter.

#### **I INTRODUCTION**

High power and high step-up isolated DC-DC converters have been widely employed in the green energy systems. In Power electronics engineering, a DC-DC converter is a circuit, which converts a source of direct current from one voltage to another. In many DC-DC converter applications, output isolation may be needed to implement depending on the type of application to meet safety standards to provide impedance matching. This galvanic isolation is necessary to achieve a flexible system reconfiguration.

DC-DC converter is a device that accepts a DC input voltage and produces a DC output voltage. Typically the output produced is at a different voltage level than the input. In addition, DC-DC converters are used to provide noise isolation, power bus regulation, etc. This is a summary of some of the popular DC-DC converter topologies. In many DC-DC applications, multiple outputs are required and

output isolation may need to be implemented depending on the application. In addition, input to output isolation may be required to meet safety standards and provide impedance matching. The above discussed DC-DC converter can be adapted to provide isolation between input and output. ZVT realizes soft switching in this converter without imposing additional switching voltage and current stress and conduction loss, allowing the use of lower voltage power devices, which usually have better conduction and switching performance than higher voltage power devices. The use of the lower voltage power devices contributes to the high efficiency.

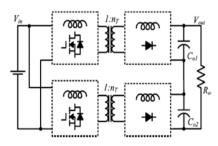

A new active clamp boost converter with coupled-inductors is proposed for high applications. The primary-parallelsecondary-series structure shown Fig 1 is employed in this paper to handle the large input current, sustain the high output voltage and extend the voltage gain. The third windings of the coupled-inductors have the function of voltage gain extension and the switch voltage stress reduction. The active clamp circuit serves for the interleaved two phases, which reduces the circuit complexity. Both the main and the auxiliary switches of the proposed converter are zero voltage transition performances during the whole switching transition and the leakage energy is recycled by the active clamp circuit. The rectifier voltage stress is reduced by the primary-parallel- secondary-series structure. The rectifier reverse-recovery problem is alleviated by the leakage inductance.

The primary-parallel-secondary-series structure shown in Fig 1 is implemented in this paper to sustain the high secondary voltage. The interleaved switch gate signals are applied to reduce the current ripple and share the input current. The secondary side is in series to reduce the rectifier voltage stress

Fig1.: Primary-series secondary parallel structure of the proposed converter

The concept of coupled inductor is widely adopted to extend the voltage gain in high step-up conversion or to avoid the extreme duty cycle in high step-down VR applications. This concept is employed to deduce the proposed zero voltage transition (ZVT) interleaved boost converter in this paper for high step-up conversion. The coupled inductors of the converter can serve as an isolation transformer, which reduces the numbers of the magnetizing components. Meanwhile, the third winding of the coupled inductors extends the voltage gain and reduces the primary switch voltage stress. With some topology variations, only one set of clamp circuit is required to serve for the interleaved two phases, which reduces the circuit complexity and improve the power density. Both the main switches and the auxiliary switch are operated with ZVT performance during the whole switching transition. Also, the leakage energy is recycled and the voltage spikes are absorbed by the active clamp circuit. The large primary current is distributed by the interleaved structure and the high secondary voltage stress is sustained by the series structure. The rectifier reverse-recovery problem is alleviated by the leakage inductance of the coupled inductors. The technique used in this paper is soft-switching and is attractive to reduce the switching losses, improve the power density and reduce the high output voltage stress. Hence the converter system has high accuracy and stability. The complexity of the circuit is reduced by using just three MOSFET switches compared with more number of switches which causes high stress and losses in converter circuits.

#### **APPLICATIONS**

ZVT dc-dc converters will be widely used in various applications such as

- 1. Energy storage system with galvanic isolation

- 2. Traction drive of hybrid fuel cell system

- 3. Residential fuel cell generation

- 4. DC UPS and industrial applications

- 5. Aerospace power systems

- 6. Electric vehicles and battery chargers

- 7. Electrolyser system

- 8. High step-up applications

## II PROPOSEDCONVERTER PRINCIPLE AND OPERATION

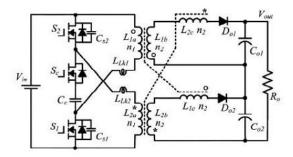

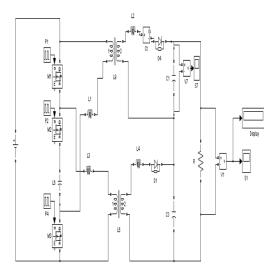

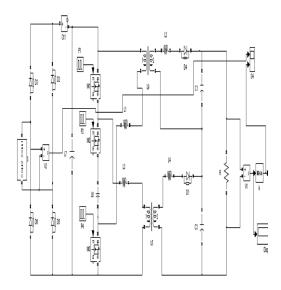

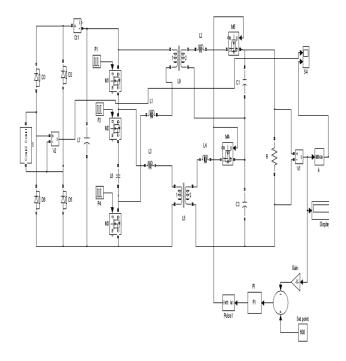

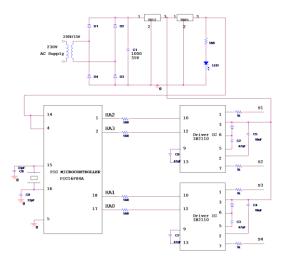

Fig 2.1 Proposed converter circuit

Flyback converters are attractive converters for lowpower, isolated voltage regulation applications. Interleaved flyback converters can be employed to reduce the current ripple and handle a large power. The two secondary sides are in series to extend the voltage gain and reduce the voltage stress of the output diodes. Active clamp solution can be adopted to recycle the leakage energy and absorb the voltage spikes . The active clamp interleaved flyback converter with primary-parallel- secondary-series structure is shown in Fig. 1 In order to realize the flyback converter with a boost type in high step-up conversion, a dc voltage should be inserted between the secondary side of the coupled inductor and the output diode. The third winding of the coupled inductor of the flyback converter can be used to achieve the dc voltage source. So a novel isolated boost type ZVT converter with coupled inductors is proposed in this paper.

The second winding couples to the inductor in its phase  $(L_{1b} \text{ versus} L_{1a} \text{ and} L_{2b} \text{ versus} L_{2a})$  and the third winding couples to the inductors in another phase  $(L_{1c}\ versusL_{1a}\ andL_{1b},\!L_{2c}\ versus\ L_{2a}andL_{2b}$  ). The primary and secondary windings serve as the transformer for isolation and energy transfer. The third winding has the advantages of voltage gain extension and switch voltage stress reduction. The active clamp circuits of each phase S<sub>c1</sub>,C<sub>c1</sub> andS<sub>c2</sub>,C<sub>c2</sub> recycle the leakage energy and absorb the voltage spikes caused by the leakage inductances when the main switches turn off. The two primary sides are parallel to handle the large input current and minimize the input current ripple. The two secondary sides are in series to sustain the high output voltage stress and double the voltage gain. The ZVS turn-off of the main and the auxiliary switches are realized due to the additional parallel capacitors. The ZVS turn-on of the main and the auxiliary switches are achieved because their anti-parallel diodes are in conduction state before their turn-on gate signals coming.

The rectifier reverse- recovery problem is alleviated due to the inherent leakage inductance of the coupled inductors. The voltage stresses of the switches and the rectifiers are minimized. So it is suitable for high power and high step-up isolation conversion. However, each phase needs a set of active clamp circuit, which increases the circuit complexity and cost. Only one set of active clamp circuit is necessary. This active clamp circuit serves for the interleaved two phases. And its switching frequency is two times of the main switch switching frequency. So the circuit is simplified and the power density is improved with the similar performance. In order to simplify the analysis, the coupled inductor is modeled as a combination of a magnetizing inductor, an ideal transformer with corresponding turns ratio, and a leakage inductance in series with the magnetizing inductor.

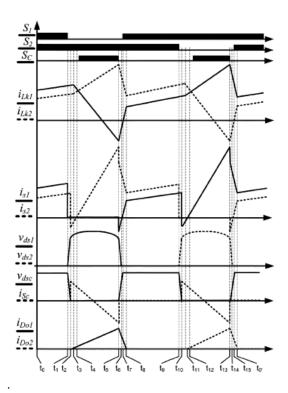

The equivalent circuit model of the presented circuit is demonstrated in Fig. 2.1, where Lm1 , Lm2 are the magnetizing inductors;  $L_{LK1}$ ,  $L_{LK2}$  are the leakage inductances;  $C_{S1}$ , and  $C_{S2}$  are the parallel capacitors, including the parasitic capacitors of the switches; Sc is the active-clamp switch; Cc is the clamp capacitor;  $S_1$  and  $S_2$  are the main switches;  $D_{O1}$  and  $D_{O2}$  are the output rectifiers;  $C_{O1}$  and  $C_{O2}$  are the output capacitors and N is the turns ratio n2/n1. The key waveforms of the presented converter are shown in Fig. 2.2

Fig 2.2Key waveforms of the Proposed converter

#### III. CONVERTER PERFORMANCE ANALYSIS

Due to the circuit symmetry of the proposed converter, it is reasonable to consider  $L_{LK1}=L_{LK2}=L_{LK}$ , Lm1=Lm2=Lm, Cs1=Cs2=Cs, Co1=Co2=Co. The detailed converter performance is analyzed as follows.

#### A. Voltage Gain Expression

Assuming that the coupled inductors are well coupled and the leakage inductance is zero, it can be drawn form the steady analysis in the above section that the magnetizing inductor is charged by the voltage Vin during the switch on time and discharged by the voltage (Vout/2N-Vin) during the switch-off time. By applying the voltage-second balance to the magnetizing inductor, the output voltage gain is given by

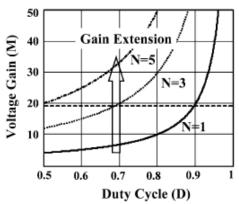

$$M = \frac{V_{OUT}}{V_{IN}} = \frac{2 \bullet N}{1 - D} \tag{1}$$

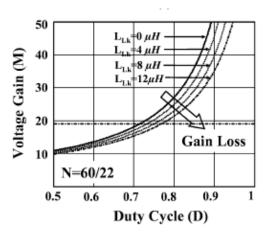

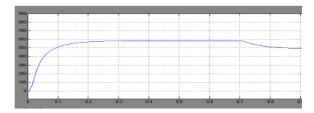

Fig. 3.1 Voltage gain at ideal situation

It is clear that the proposed converter is a boost type with high voltage gain. Fig. 3.1 shows the detailed plot of the voltage gain related to the turns ratio and duty cycle. As the duty cycle and the turns ratio increase, the voltage gain increases greatly. The operation analysis in the above section shows that the leakage inductance causes some duty-cycle loss and leads to a voltage gain loss. The duty-cycle loss is given by

$$\Delta D_{LOSS} = \frac{I_{IN} \bullet N \bullet L_{LK} \bullet f_{x}}{V_{OUT}}$$

(2)

where  $I_{\rm in}$  is the input rms current and Fs is the switching frequency. It is shown that the duty-cycle loss is proportional to the input current, the turns ratio, the leakage inductance and the switching frequency. The effect of the leakage inductance on the voltage gain is shown in Fig. 3.2. As the leakage inductance increases, the voltage gain decreases.

Fig. 3.2 Effect of the leakage inductance on gain loss

### B. Voltage and Current Stresses of the Power Devices

In order to simplify the analysis, the effect of the leakage inductance and the voltage on the clamp capacitor is taken as a constant voltage. The voltage stress and the rms current of the main switch are given by

$$V_{STRESS-MAIN} = \frac{V_{IN}}{1 - D}$$

$$I_{RMS-MAIN} = \frac{I_{IN}}{2} \sqrt{\frac{13 - (10 \bullet D)}{3}}$$

$$(4)$$

The switch voltage stress is determined by the input voltage and the duty cycle. The current stress analysis should consider the current reflected effect. The voltage stress and the rms current of the clamp switch is given by

$$V_{STRESS-CLAMP} = \frac{V_{IN}}{1 - D}$$

$$I_{STRESS-CLAMP} = \frac{I_{IN}}{2} \sqrt{\frac{2 \cdot (1 - D)}{3}}$$

(6)

.The voltage stress of the clamp switch is the same as that of the main switch. The rms current of the clamp capacitor is equal to that of the clamp switch. The voltage stress and the rms current of the output diode is given by

$$V_{STRESS-DIODE} = V_{OUT} \tag{7}$$

$$I_{RMS-DIODE} = \frac{I_{IN}}{N} \sqrt{\frac{\left(1-D\right)}{3}} \tag{8}$$

The voltage stress of the diode is the output voltage and the rms current of the diode is determined by the input current, the turns ratio, and the duty cycle.

#### C. ZVT Soft-Switching Performance

Both the main switches and the auxiliary switch are achieved the ZVT soft-switching performance during the whole switching period, which reduces the switching losses greatly. Meanwhile, the rectifier reverse-recovery problem is alleviated due to the leakage inductance. The output diode turn-off current falling rate is given by

$$\frac{di_{Do}(t)}{dt} = \frac{V_{OUT}}{2 \bullet N^2 \bullet L_{LK}}$$

(9)

The ZVS-off of the main switches and the clamp switch is realized due to the parallel capacitors  $C_{\rm s1}$  and  $C_{\rm s2}$ . The ZVS-on of the clamp switch is achieved naturally because its anti-parallel diode is in conduction state before its gate-on signals. The ZVS-on of the main switches is realized if the leakage energy is larger than the energy stored in the parallel capacitor when the main switches turn off. That is

$$L_{LK} \ge \frac{C_S \bullet V_{OUT}^2}{N^2 \bullet I_{IN}^2} \tag{10}$$

which can be used to determine the leakage inductance design. The ZVS-on of the main switches depends on the parallel capacitor Cs, the output voltage Vout, the turns ratio N and the input current  $I_{\rm in}$ . It can be seen that the required leakage inductance decreases as the input current and the turns ratio increase.

#### D. Limitation of the Turns Ratio

From the steady operation analysis, it can be concluded that there is an absolute condition that must be met in the proposed converter: The duty cycle should be exceeded 0.5. This condition is expressed as

$$N \leq \frac{V_{OUT}}{4 \bullet V_{IN}}$$

(11)

#### IV SIMULATION RESULTS

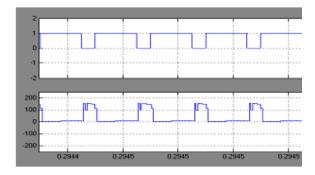

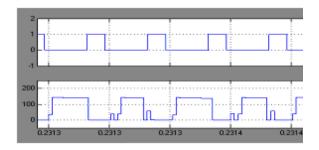

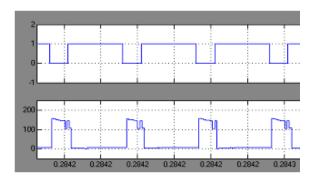

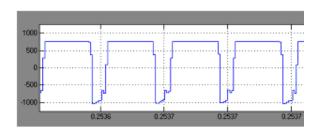

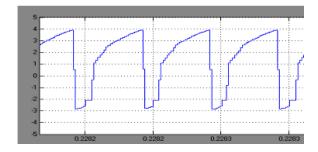

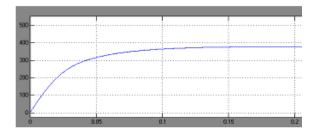

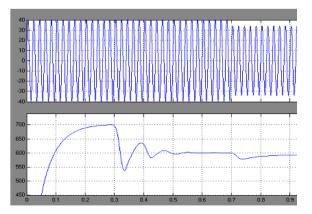

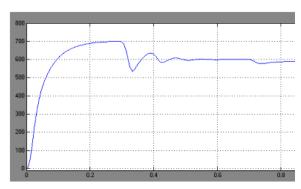

ZVT Boost DC-DC converter is modelled using the blocks of MATLAB Simulink and the results are presented in this section. Scope 1 is connected to display the driving pulses. Scope 2 is connected to

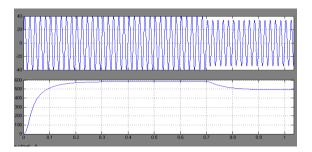

display the output voltage. The circuit of ZVT Boost DC-DC converter is shown in Fig 4.1. Driving pulse and voltage across switch M1 is shown in Fig 4.2 Driving pulse and voltage across switch M2 is shown in Fig 4.3 .Driving pulse and voltage across switch M3 is shown in Fig 4.4. Transformer output voltage is shown in Fig 4.5. Current through the inductor L2 is shown in Fig 4.6. Voltage across the capacitor C1 is shown in Fig 4.7.Output voltage is shown in Fig 4.8 output current is shown in Fig 4.9. Open loop circuit diagram is shown in Fig 4.10. Input and output voltage with disturbance for open loop is shown in Fig 4.11. Output voltage with disturbance for open loop is shown in Fig 4.12. closed loop circuit diagram is shown in Fig 4.13. Input and output voltage with disturbance for closed loop is shown in Fig 4.14. Output voltage with disturbance for closed loop is shown in Fig 4.15.

#### Isolated zvt boost converter

Fig 4.1 Circuit diagram

Fig 4.2 Driving pulse and voltage across switch M1

Fig 4.3 Driving pulse and voltage across switch M2

Fig 4.4 Driving pulse and voltage across switch M3

Fig 4.5 Transformer output voltage

Fig 4.6 Current through inductor L2

Fig 4.7 voltage across capacitor c1

Fig 4.8 output voltage

Fig 4.9 output current

Isolated ZVT boost DC-DC converter is simulated for both open loop circuit and closed loop circuit. with output disturbance applied at the time instant of  $t=0.7\,$  micro second .

Fig 4.10 Open loop circuit diagram

Fig 4.11 Input and output voltage with disturbance

Fig 4.12 Output voltage with disturbance

Fig 4.13 Closed loop circuit diagram

Fig 4.14 Input and output voltage with disturbance

Fig 4.15 Output voltage with disturbance

It is noted that there is a drop in output voltage due to the disturbance applied to the open loop system. In a closed-loop control system, a sensor monitors the output and feeds the data to a proportional Integral circuit which continuously adjusts the control input as necessary to keep the control error to a minimum value of the desired voltage. Feedback on how the system is actually performing allows the controller to dynamically compensate for disturbances. The simulation results of the proposed converter with output disturbance applied at the time instant of t=0.7. and noted that the output voltage is maintained constant always.

From the above discussion closed loop system gives stabilized output even though disturbance.

#### V EXPERIMENTAL RESULTS

The hardware for ZVT Boost DC-DC converter is fabricated in the laboratory with resistive load. Converter uses three MOSFET switches using IR840. Pulses required by the MOSFET's are generated by using a PIC microcontroller 16F84A. These pulses are amplified by using a driver amplifier IC IR2110.Voltage Regulators 7812,7805 are used for supplying desired voltages to PIC controller and driver IC's. High frequency ferrite core transformer is used in the circuit for high step-up applications. Output Diodes are used to get rectified dc output. Output capacitors are small in capacity which provides boosted voltage.

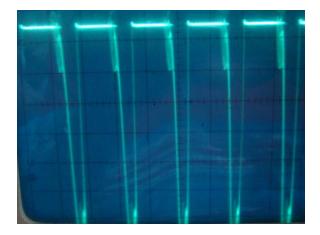

The specifications of the converter are 15V to 85V; Fs = 50Khz. The parallel capacitor is 1000 micro Farads to achieve ZVS of the switches. The switching frequency is 50 kHz to reduce the size of the passive components. Both the main switches and the auxiliary switch achieve ZVT operation during the whole switching transition. The switching losses are reduced, the efficiency is improved and the power density is increased. The switch voltage stress is about 150 V which can be noticed in the CRO. It is clear that the reverse-recovery current is reduced to nearly zero and the reverse-recovery problem is alleviated dramatically by the leakage inductance with about 12 A/s.

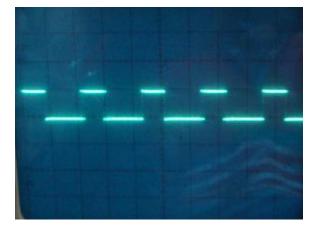

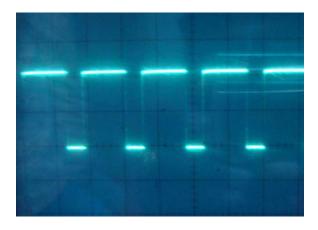

The hardware layout is shown in Fig. 5.1 The hardware consists of power circuit and microcontroller based control circuit. The pulses are generated by using the PIC microcontroller 16F84A .These pulses are amplified using the driver IC IR2110. Control circuit for generating the driving pulses is shown in Fig. 5.2. The switching pulses are shown in Fig. 5.3 The driving pulses are generated by the microcontroller are shown in Fig. 5.4. Transformer output voltage is shown in Fig. 5.5. DC output voltage is shown in Fig. 5.6.

In Hardware unit the converter uses only three MOSFET's which reduces the number of devices and makes the circuit simple in construction. Efficiency, size and cost are the advantages of the isolated ZVT boost converter.

Fig 5.1. Hardware layout

Fig 5.2 Control circuit

Fig 5.3 Switching pulse

Fig 5.4 Driving pulse

Fig 5.5 Transformer output voltage

Fig 5.6 DC Output voltage

#### VI CONCLUSION

ZVT Boost DC-DC converter is simulated and tested in laboratory. This paper introduces a primaryparallel-secondary-series ZVT boost converter for high step-up applications. The additional winding of the coupled inductors extends the voltage gain and reduces the switch voltage stress. The leakage energy is recycled by the active clamp circuit. The active clamp circuit serves for the interleaved two phases, which reduces the circuit complexity. Both the main switches and the clamp switch are ZVT during the whole switching transition. The rectifier voltage stress is reduced by the primary-parallel-secondary-series structure. The rectifier reverse-recovery problem is alleviated by the leakage inductance.

The switching losses and the output diode reverse- recovery losses are reduced greatly, which is important for high-frequency and high-power applications. The EMI noise is suppressed significantly, and the reverse-recovery losses are reduced greatly. This improves the efficiency of the converter. The results show that the proposed converter has better performance than the other converters at higher switching frequency. The analysis and experimental results show that the proposed converter is a suitable for high step-up and high-power-density applications.

#### **REFERENCES:**

- [1] R. J. Wai and R. Y. Duan, "High step-up converter with coupled-inductor," *IEEE Trans. Power Electron.*, vol. 20, no. 5, pp. 1025–1035, Sep. 2005.

- [2] X. Huang, X. Wang, T. Nergaard, J. S. Lai, X. Xu, and L. Zhu, "Parasitic ringing and design issues of digitally controlled high power interleaved boost converters," *IEEE TransPower Electron.*, vol. 19, no. 5,pp. 1341–1352, Sep 2004.

- [3] C. Liu, A. Johnson, and J. S. Lai, "A novel three-phase high-power soft-switched DC/DC converter for low-voltage fuel cell applications,"

- *IEEE Trans. Power Electron.*, vol. 41, no. 6, pp. 1691–1697, Nov.–Dec.2005.

- [4] Q. Zhao and F. C. Lee, "High-efficiency high step-up DC/DC converters," *IEEE Trans. Power Electron.*, vol. 18, no. 1, pp. 65–73, Jan. 2003.

- [5] L. Yan and B. Lehman, "An integrated magnetic isolated two-inductorboost converter: Analysis, design and experimentation," *IEEE Trans.Power Electron.*, vol. 20, no. 2, pp. 332–342, Mar. 2005.

- [6] L. Zhu, "A novel soft-commutating isolated boost full-bridge ZVS-PWM DC-DC converter for bidirectional high power applications," *IEEE Trans. Power Electron.*, vol. 21, no. 2, pp. 422–429, Mar.2006.

- [7] C. Iannello, S. Luo, and I. Batarseh, "Full bridge ZCS PWM converter for high-voltage high-power

- applications," *IEEE Trans. Aerosp. Electron.Syst.*, vol. 38, no. 2, pp. 515–526, Apr. 2002.

- [8] R. Watson and F. C. Lee, "A soft-switched, full-bridge boost converter employing an active-clamp circuit," *Proc. IEEE PESC'96*, pp. 1948–1954, 1996.

- [9] E. S. Park, J. C. Sung, J. M. Lee, and B. H. Cho, "A soft-switching active- clamp scheme for isolated full-bridge boost converter," *Proc. IEEE APEC'04*, pp. 1067–1070, 2004.

- [10] L. Zhu, K. R. Wang, F. C. Lee, and J. S. Lai, "New start-up schemes for isolated full-bridge boost converters," *IEEE Trans. Power Electron.*, vol. 18, no. 4, pp. 946–951, Jul. 2003.

- [11] C. Wang, Y. Kang, B. Lu, J. Sun, M. Xu, W. Dong, F. C. Lee, and W. C. Tipton, "A high power-density, high efficiency front-end converter for capacitor charging applications," *Proc. IEEE APEC* '05, pp. 1258–1264, 2005.

- [12] R. Liu, C. Q. Lee, and A. K. Upadhyay, "Experimental investigation of the LLC-type parallel resonant converter," *Proc. IEEE APEC'90*, pp. 723–732, 1990.

- [13] J. F. Lazar and R. Martinelli, "Steady-state analysis of the LLC series resonant converter," *Proc. IEEE APEC'01*, pp. 728–735, 2001.

- [14] B. Yang, F. C. Lee, and M. Concannon, "Over current protection methods for LLC resonant converter," *Proc. IEEE APEC'03*, pp. 605–609, 2003.

- [15] R. Liu and C. Q. Lee, "Series resonant converter with third-order commutation network," *IEEE Trans. Power Electron.*, vol. 7, no. 3, pp. 462–468, Jul. 1992.

- [16] B. Lu, W. D. Liu, Y. Liang, F. C. Lee, and J. D. VanWyk, "Optimal design methodology for LLC resonant converter," *Proc. IEEE APEC'06*, pp. 19–23, 2006.

#### **BIOGRAPHIES**

**R. Samuel Rajesh Babu** has obtained his B.E degree from Madras University in 2003. He has obtained his M.E degree from Anna University in 2005. Presently he is doing his research at Sathyabama University. His area of interests is DC - DC converters.

**Dr. Joseph Henry** has obtained his B.E Degree from Madras University in 1960.He obtained his M.E degree from IIT-Bombay in 1964. He obtained his Ph.D degree from IIT Delhi in 1978. Presently he is a professor in Vel Tech University. His areas of interest are Power Electronics and Digital Protection