## Design and Realization of Internal Model Control Scheme for Single Phase Power Factor Correction with DC-DC SEPIC Converter

## S.Durgadevi<sup>1\*</sup>, M.G.Umamaheswari<sup>2</sup>

\*1 Research Scholar, Department of Electrical and Electronics Engineering , Rajalakshmi Engineering College, Chennai-602105, Tamil Nadu, India.& Assistant Professor, Department of Electronics and Instrumentation Engineering, Sri Sairam Engineering College, Chennai 600044, Tamil Nadu, India.

(e-mail: durgadevi.ei@sairam.edu.in)

<sup>2</sup>Professor& Head, Department of Electrical and Electronics Engineering, Rajalakshmi Engineering College affiliated to Anna University, Chennai 602105, Tamil Nadu, India

Abstract: This paper proposes a novel methodology known as internal model control (IMC) to design the Controllers used in Single Phase power factor correction using DC-DC SEPIC (Single Ended Primary Inductance Converter). In this paper, an IMC strategy is applied to design the Proportional Integral Control parameters used in the voltage and current controllers. The closed loop implementation of Single phase power factor correction involves two loops which are namely voltage and current loops. These two loops are implemented with PI controllers .Hence it becomes mandate to design the PI controllers with appropriate tuning methods. The various performance measures such as %THD, Power factor and effective tracking of output voltage for load disturbance, set point and supply voltage variations are verified using MATLAB /Simulink tool.

**Key words:** Power factor correction, IMC, %THD, Unity power factor

#### 1. Introduction

In switched mode power supply applications, there is a necessity to design power factor correction circuit with DC-DC power converters of almost unity power factor and less harmonic distortion [1]. Hence it is proposed to design a single phase power factor corrector with DC-DC SEPIC Converter .DC-DC SEPIC converter has more advantages than other power converters such as Buck, Boost and Cuk Converters in terms of its operating characteristics like continuous input and output currents ,and increase/ decrease of output voltage level with positive polarity[2]. There are various conventional tuning methods are proposed by various researchers for finding the PI controller coefficients [3-5]. To overcome some limitations in the existing tuning methods, it is decided to propose a tuning strategy based on the model of the controller. Since DC-DC SEPIC converter is of fourth order, its approximate second order model is used as a model of the converter. The application of this proposed closed loop system brings down the total harmonic distortion (THD) level to less than 5 % as per IEEE and IEC standard [6]. The various performance measures such as %THD, Power factor and effective tracking of output voltage for set point and supply voltage variations are verified using MATLAB /Simulink tool.

## 2. Operation, Design and modeling of DC-DC SEPIC Converter

## A. Operation of DC-DC SEPIC Converter

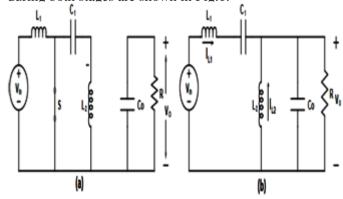

The operation of DC-DC SEPIC converter is explained in two operating modes [7, 8]. (i) Switch ON stage (ii) Switch OFF stage. The equivalent circuits during both stages are shown in Fig.1.

Fig.1 Equivalent circuit (a) during switch ON (b) OFF stage

During switch ON- stage, the diode D is in OFF stage. The current flowing through the input and the output inductors ( $L_1$  and  $L_2$ ) increases linearly and the coupling capacitor  $C_1$  transfers energy to the load. During switch OFF stage, the diode D gets turned ON. The current flowing through the inductor  $L_1$  and  $L_2$  now decreases and the load current is provided by an output inductor  $L_2$ .By applying KVL and KCL, the state equations are written which are then used to obtain equivalent state matrices.

#### **B.Design of DC-DC SEPIC Converter**

The design specifications of the DC-DC SEPIC converter is obtained as follows [9-11]. The converter is designed for a maximum power rating of 200 W with a duty cycle of 0.67. The following Table I gives the values of design specifications of the DC-DC SEPIC Converter.

Table I – Design Specifications

| Parameters                             | Specifications |

|----------------------------------------|----------------|

| Switching Frequency                    | 50Khz          |

| Input Voltage (Vrms)                   | 50 V           |

| Load Resistance(RL)                    | 50 Ohm         |

| Source Current (IS)                    | 6 A            |

| Input Inductor(L1) Output Inductor(L2) | 2mH<br>1mH     |

| Input Capacitor                        | 10μF           |

| Output Capacitor                       | 6000 μF        |

Since DC-DC SEPIC converter is of fourth order type, its transfer function is obtained by substituting the calculated inductor and capacitor values in the averaged state space equation .The fourth order transfer function is then obtained as follows:

$$G_4(s) = \frac{27500s^2 + 2.44e^{-11} s + 1.843e^{12}}{s^4 + 3.33s^3 + 5.036e^{07}s^2 + 1.678e^{08}s + 9.075e^{11}}$$

(1)

The fourth order transfer function model is converted to second order model for simplifying the controller design .Hence the fourth order model is converted to second order using Pade's Approximation. The second order transfer function obtained is as follows:

$$G_2(S) = \frac{-2.492e^{-6}s + 2.027}{5.553e^{-5}s^2 + 1.835e^{-4}s + 1}$$

(2)

The above second order transfer function is represented into pole - zero form which is as follows:

$$zpk[G_2(S)] = \frac{-0.044872(s - 8.134e^5)}{s^2 + 3.309s + 1.801e^4}$$

(3)

# 3. Closed loop Implementation of the proposed control strategy with IMC

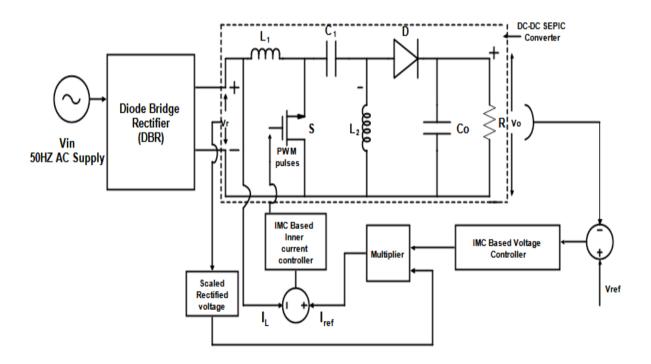

The closed loop implementation of the proposed method is shown in Fig.2

Fig.2 Closed loop implementation of proposed scheme with IMC.

It shows the PFC using cascade method which has two loops. One is outer loop for controlling the output voltage and inner current loop. The outer and inner PI controllers play a major responsibility of providing power factor correction with almost unity power factor and acceptable percent Harmonic distortion. Hence the major design aspect involves in choosing the appropriate PI controller co-efficients. Internal model control is one of the techniques designed for obtaining the parameters of PI controller. The outer PI controller output is used for generating reference for an inner current loop using multiplier approach. The generated reference current is then compared with an input inductor current. This current error signal at one input of the comparator and other input with carrier pulse of required switching frequency generates PWM pulses which are then used to trigger the MOSFET switch.

## A. Design of controllers with IMC

Internal Model Control is one of the model-based control schemes proposed for an efficient and robust controller design. As the name implies, the controller has model of the process internally. The main advantage of IMC is that very simple structure and design procedure [12-14]. The design

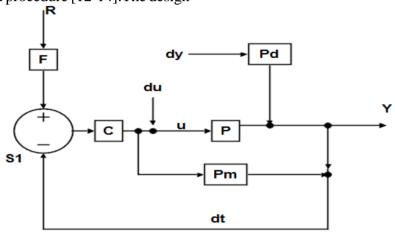

of IMC involves connecting model of the process across the actual process. The controller thereby achieving dynamic inversion of the model of the process. The structure of IMC is shown in Fig. 3 P is actual process, Pm is the model of process, and C is the IMC controller. The controller objective is to make output Y to track reference R. The following are the steps involved in the design of IMC controller. (i) The model of the process Pm is divided into Pd which consists of time delays and right-half-plane zeros and transfer function Pm- with minimum phase characteristics. (ii) a low pass filter whose time constant plays a vital role to make the system to be robust with improved stability.

Fig.3 IMC Controller Structure

The selection of this low pass filter is based on the following transfer function

$$G_f(s) = \frac{1}{(\tau_f s + 1)^n}$$

(4)

IMC control transfer function is given below  $C(s) = G_{-}(S)G_{f}(S)$  (5)

The general feedback controller can be obtained from IMC controller using following equation.

$$K = \frac{C}{1 - GC} \tag{6}$$

Hence it is more important to design suitable feedback controller such that the system should be able to respond to changes in output voltage for load and line variations thereby achieving voltage regulation to desired value. The second order model of DC-DC converter can be brought to PID controller form using IMC design procedure.

$$C(S) = K_C \left(1 + \frac{1}{sT_i}\right)$$

Where  $K_C = \frac{2\zeta T}{k(\beta + \tau_f)}$  ;  $T_i = 2\zeta T$  (7)

The general transfer function in time constant form is given as

$$=\frac{K(-\beta s+1)}{\tau^2 s^2 + 2\xi \tau s + 1}$$

(8)

The transfer function (2) can be simplified to time constant form as given below:

$$[G_2(S)] = \frac{2.021(-1.129e^{-6}s + 1)}{1 + 1.834e^{-4}s + 5.552e^{-5}s^2}$$

(9)

Where k= 2.021,  $\beta$  =1.129e-6;  $\xi$ =0.0123 and  $\tau_f$ =0.117. By substituting these values in Eq. (7) the values of Kc and Ti are found.

#### 4. Simulation Results

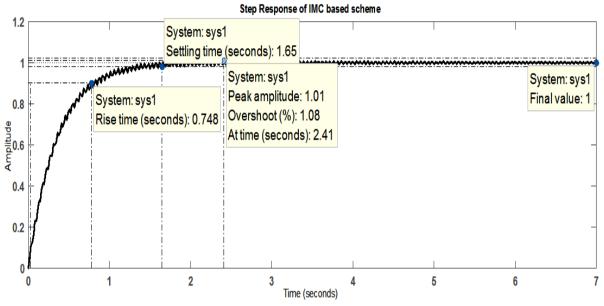

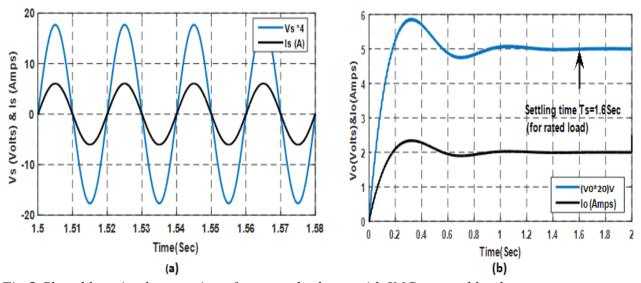

This section presents the simulation results of proposed scheme for rated and various loading conditions. The dynamic response of the proposed IMC based closed loop scheme is shown in Fig.4.

### A. Dynamic response of the proposed system

Fig.4 Dynamic response for IMC based closed loop control

## B.Closed loop simulation result

This section gives the simulation result for closed loop IMC for rated load and set point variations. Fig. 5 shows the simulation waveforms

at rated load. The output settles at t=1.6 Sec with % THD=0.125 and almost unity power factor.

Fig. 5 Closed loop implementation of proposed scheme with IMC at rated load.

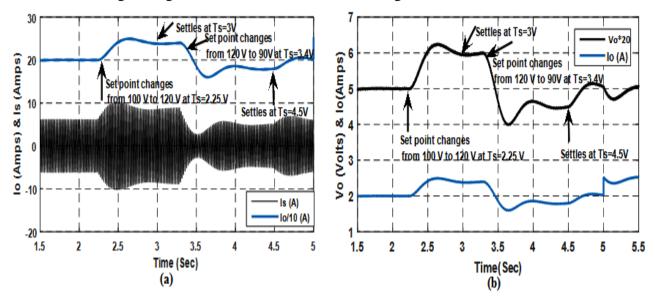

Fig.6 shows the simulation waveforms for set point variations. The set point is changed from

100 V to 120 V at t=2.25 sec and settles at 120 V at t= 3 sec with a settling time of Ts=0.75sec .At t

=3.4 sec the voltage changes from 120 V to 90 and

the voltage settles at t=4.5 sec.

Fig.6 Closed loop implementation of proposed scheme with IMC for set point variations.

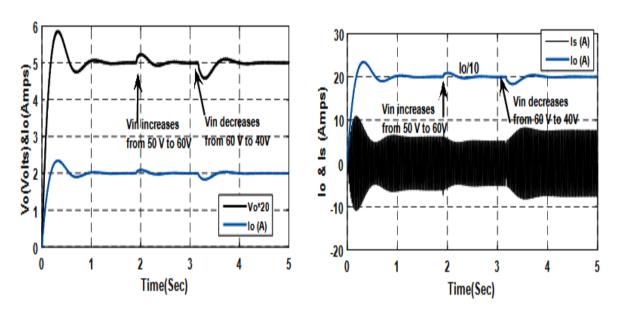

Fig.7 presents the output voltage and current waveforms for line voltage variations. From the Fig.7, it is clearly evident that output gets back to

reference voltage even after it is subjected to line variations.

Fig. 7 Closed loop implementation of proposed scheme with IMC for line voltage variations.

#### **Conclusion**

The performance of IMC based closed loop control of single Phase power factor correction with DC-DC SEPIC converter is realized .The results reveal that the output voltage settles

quickly at 1.6 sec with % THD of 0.125 for rated load. It also responds rapidly for load, line voltage and set point variations with almost unity power factor.

#### References

- [1] Gracia, Single phase Power factor Correction- A survey, IEEE Transactions On Power Electronics, Vol. 18, No. 3, (2003), 749-755.

- [2] Priscila Faccode Melo, Roger Gules, Eduardo Felix Ribeiro, et al'A Modified SEPIC Converter for High-Power-Factor Rectifier and Universal Input Voltage Applications', IEEE transactions on Power electronics, vol. 25, no.2, Feb 2010. pp:310 321

- [3] Mustafa, et.al,. 'An Improved Topology of SEPIC Converter With Reduced Output Voltage Ripple, IEEE Transactions on Power Electronics,vol.23, No. 5,2008 pp.310-321.

- [4] Andrea Cantillo, et.al, 'Stability Issues in Peak-Current-Controlled SEPIC', IEEE Transactions on Power Electronics,vol.26, No. 2,2011. pp. 551-562.

- [5] Laszlo Huber, Misha Kumar, Milan M. Jovanovi, 'Performance Comparison of PI and P Compensation in DSP-Based Average-Current-Controlled Three-Phase Six-Switch Boost PFC Rectifier', IEEE transactions on power electronics, vol. 30, no. 12, December 2015 pp:7123 7137

- [6] 519-2014- IEEE Recommended Practice and Requirements for Harmonic Control in Electric Power Systems .June 11- 2014 .pp:1 29

- [7] Lamar.D.G Zuniga J.S, Alonso A.R,.etal, 'A Very Simple Control Strategy for Power Factor Correctors Driving High-Brightness LEDs' IEEE transactions on power electronics, vol. 24, no. 8, August 2009.pp: 2032 2041

- [8] Tomislav Pavlovic, Toni Bjazi,Zeljko Ban, 'Simplified Averaged Models of DC–DC Power Converters Suitable for Controller Design and Microgrid Simulation',IEEE transactions on Power electronics, vol. 28, no.7, July 2013. pp: 3266 3275

- [9] Mustafa, et.al,. 'An Improved Topology of SEPIC Converter With Reduced Output Voltage Ripple, IEEE Transactions on Power Electronics,vol.23, No. 5,2008 pp.310-321.

- [10] G.Spiazzi, P. Mattavelli, 'Design criteria for power factor preregulators based on Sepic and cuk converters in continuous conduction mode', Published by IEEE in Industry Applications Society Annual Meeting, 1994., pp:1084 1089 vol.2

- [11]Wei Gu, Dongbing Zhang, 'Designing a SEPIC Converter', Excellent Design Guidelines, National Semiconductor in Application Note, April, 2008, pp. 1-6. Ltd.

- [12] Mehrdad Yazdanian, Graduate Student Member, IEEE, and Ali Mehrizi-Sani, Member, IEEE' Internal Model-Based Current Control of the RL Filter-Based Voltage-Sourced Converter' IEEE Transactions on Energy Conversion, VOL. 29, NO. 4, DECEMBER 2014 pp.873-881

- [13] P.V. Gopi Krishna Rao, M.V. Subramanyam & K. Satyaprasad 'Design of internal model control-proportional integral derivative controller with improved filter for disturbance rejection' Systems Science & Control Engineering, Published by Taylor & Francis. Vol. 2, pp. 583–592, Aug 2014.

- [14] Zhenyu Zhao 'Adaptive Internal Model Control Based Ripple Rejection for Improved Response of PFC Rectifiers' IEEE 30th Canadian Conference on Electrical and Computer Engineering (CCECE) ,2017