# A SITO DC-DC CONVERTER HYBRID CASCADED MULTILEVEL INVERTER TOPOLOGY FOR STAND-ALONE PV APPLICATIONS

#### G. S. ARUNKUMAR

Research Scholar, Anna University, Chennai arunbe 20@ gmail.com

# N. P. ANANTHAMOORTHY

Professor, Department of EEE, Hindusthan College of Engineering and Technology, Coimbatore npaeee16@gmail.com

Abstract: The Photovoltaic (PV) is an unavoidable segment in renewable energy based power generation system. The two stage power conversion is a best pay tribute to stone alone such as EV charging station or grid-connected PV power system Nevertheless, the power converters design and control integration must be prized in order to achieve the efficiency and reliability. In this paper, a new single input triple output non-isolated DC-DC boost converter (SITO DC-DC converter) and a 15 level reduced switch hybrid Hbridge multi-level inverter (MLI) are designed for a standalone PV system which is most suitable to both domestic and industrial applications. To interface the DC - DC converter and DC-AC converter, a new hybrid pulse width modulation technique (PWM) is proposed which reduces the total harmonic distortion (THD) of the output voltage and mainly SITO converter reduces the voltage balancing problem in MLI while converting DC to AC. The proposed system is simulated using MATLAB/Simulink system software and laboratory scale setup is build and implemented by using SPARTAN 3 DSP controller. The simulation and experimental results are confirmed proposed converters

Index Terms: SITO DC –DC converter, cascaded H-bridge MLI, Pulse Width Modulation (PWM) technique, total harmonic distortion (THD), SPARTAN 3 DSP controllers.

## 1. Introduction

Usage and demand of renewable energy sources (RES) is increasing day by day in order to reduce the dependency on conversional energy source which plays a major role in the climatic change. Among the various RES, more research and more focus is turned towards photovoltaic (PV) system because of reliability, less impact on environment and cost factor involved in the energy production process. Standalone PV system such as EV charging station and other industrial application is been encouraged in all the countries. Energy conversion process involved in standalone PV system is mainly depended on converters which includes DC to DC and DC to AC. Obviously, designing appropriate PWM technique for the proposed DC to AC converters in order to reduce the harmonics of the output is being a big challenge.

Zeng, and Huafang Guo designed a nine level inverter with less switching devices and voltage sources [1]. It is achieved by connecting the two capacitors and a voltage source in series and parallel. Rasoul Shalchi Alishah, Seyed Hossein Hosseini, Ebrahim Babaei, and Mehran Sabahi proposed an

optimized laddering technique is incorporated to design cascaded MLI structure [2] in which a new optimized pulse width modulation technique is proposed to improve the number of levels with less switching devices and DC sources. Amir Taghvaie, Jafar Adabi, and Mohammad Rezanejad introduced a new circuit topology of step-up MLI with a single DC source [3]. In that topology, by controlling the charging and discharging of switched capacitors in predetermined time, the number of levels in the output voltage is obtained. Amin Gholizad and Murtaza Farsadi proposed a improved staircase modulation for MLI [4] in which a solution for SOC for storage cells is examined. Reduced switch MLI topologies are proposed in which DC sources are connected in series and parallel [5-7] (MLISPC) and a circuit which consists of four diodes and a switch replaces the series and parallel combination of switches [8] in the MLISPC. For the same level of output voltage, only two voltage sources are needed in [8]. The proposed MLI topologies in [9-14] can be used for the PV systems application like electric hybrid vehicles etc. In all the above literatures, switching devices used to construct MLI is large and the THD value is also somewhat high. Hamed Nadeni and Ralando Burgos proposed a new circuit topology of modular multilevel converter (MMC) for photovoltaic system [15,29] in which two arm inductors are replaced with the transformer in order to reduce the circulating current and provides 50% reduction in voltage rating of power devices and capacitor size in comparison with basic MMC topology.

Irfan Ahmed proposed a simplified space vector modulation technique for MLI [16]. Emad Samadaei proposed a new E-type module for asymmetrical MLI with four unequal DC source and 10 switches to produce 13voltage levels [17]. And SHE-PWM technique has been used here to achieve high quality output voltage with lower harmonics. Jalal Amini made a general control strategy for multilevel converters (MLC) based on Knapsack problem [18] in which he has given the methods to choose appropriate control strategies for MLI. Viju Nair proposed a new method to generate more number of levels in the voltage waveform by stacking MLC [19] with lower voltage space vector structures thereby he reduced the rating of switching devices.

Elyas Zamiri proposed a new switched capacitor MLI which generates a great number of output voltage levels with optimum number of components for both symmetric and asymmetric type of DC voltage sources [20]. This is having the ability of boosting and charging of capacitors as self-balancing using binary asymmetrical algorithm. Arun Rahul proposed a closed loop capacitor voltage control strategy for cascaded MLI topologies which is fed with single DC supply [21]. Raghavendra Reddy Karasani proposed a 3-phase hybrid cascaded modular MLI topology with reduced number of switching devices for solar energy conversion system [22] in which transformer-less operation improves the quality of the output power. Ahmed Salem propose a new three phase modular MLI in which the output voltage levels can be increased by adding additional cells without increasing voltage stresses across power switches [23]. For this operation, both sinusoidal and staircase PWM have been used.

KehuYhang and Chi Zhang have done an experiment on 13level cascaded H-bridge converter in which they developed an unified selective harmonic elimination approach [24] and they formulated 3 different switching patterns and they applied these patterns on 13level inverter. Soek Min Kim designed a modified left shift PWM for inverters [25] which is for open and short circuits device faults. VenuSonti and Sachin Jain proposed a new pulse width modulation with reduced number of carrier waveforms for five level cascaded MLI to reduce the leakage current of PV array [26], electromagnetic inference and filter requirement without adding any extra switches. MaharanQuraan evaluated the performance of modular MLC with integrated battery cells used as traction drives for battery electric vehicles [27]. Mohamed Trabelsi designed a finite control set model predictive control for grid-tied packed U-cells MLI [28] with reduced of passive and active components in which he achieved low THD value in the output voltage level while balancing the capacitor voltages [31].

In this paper, a 15level hybrid cascaded MLI is designed with 10 switching devices and to reduce the voltage balancing problem, a new SITO DC-DC converter is designed for PV system application. In this proposed system, a PV array is designed and the output from PV system is fed to 15level MLI through SITO DC-DC converter which is simulated using MATLAB/SIMULINK and the results are presented here

# 2. Proposed Hybrid Multilevel Inverter with SITO DC-DC Boost Converter and PV System

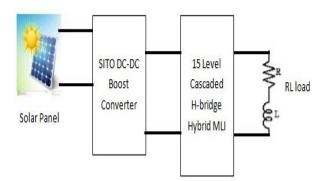

Fig. 1 shows the block diagram of proposed system. In which the output of solar panel is given to SITO DC-DC converter. Then the boosted and splitted output voltage from SITO DC-DC converter is given to 15level inverter to drive the RL load.

Fig 1. Block diagram of proposed system

The proposed system includes SITO DC-DC converter in order to reduce the voltage balancing problem which arises in conventional MLI. The proposed hybrid cascaded MLI generates 15levels of output voltage which can be used to drive the induction motor in industrial applications.

#### A. Photovoltaic Array Design

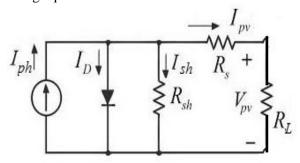

Fig. 2 shows the equivalent circuit of a solar cell. PV panel is designed for specific rating by using the following equations.

Fig 2. Equivalent circuit of a solar cell

$$I_{ph} = \left[I_{sc} + k_i \left(T_c - T_{ref}\right)\right] \left(\frac{S}{1000}\right) \tag{1}$$

$$I_{rs} = \frac{I_{sc}}{\left[\exp\left(\frac{qV_{oc}}{N_s KAT_c}\right) - 1\right]}$$

(2)

$$I_{s} = I_{rs} \left(\frac{T_{c}}{T_{ref}}\right)^{3} \left[ \exp \left(\frac{qE_{g}\left(\frac{1}{T_{ref}} - \frac{1}{T_{c}}\right)}{KA}\right) \right]$$

$$I_{pv} = N_{p}I_{ph} - N_{p}I_{s} \left[ \exp \left(\frac{q(V_{pv} + I_{pv}R_{s})}{N_{s}AKT_{c}}\right) - 1 \right] - \left(\frac{V_{pv} + I_{pv}R_{s}}{R_{sh}}\right)$$

(4)

The following considerations have been made to design the PV panel in order to get 70V and 2A as output from the 210Watts PV panel which is shown in table I.

Table 1 Parameters Considered for PV System Design

| S.No | Parameters                                                 | Ratings                             |

|------|------------------------------------------------------------|-------------------------------------|

| 1    | I <sub>sc</sub> (Short circuit current)                    | 2.916A                              |

| 2    | V <sub>oc</sub> (Open circuit voltage)                     | 72V                                 |

| 3    | T <sub>op</sub> (Operating Temperature)                    | 25°C                                |

| 4    | T <sub>c</sub> (Critical Temperature)                      | (273+T <sub>op</sub> ) in<br>Kelvin |

| 5    | $T_{ref}(Reference\ Temperature)$                          | (273+25) in<br>Kelvin               |

| 6    | q(electron charge)                                         | 1.602*10 <sup>-19</sup> C           |

| 7    | K(Boltzmann Constant)                                      | 1.3805*10 <sup>-23</sup><br>J/K     |

| 8    | A(Ideality Factor)                                         | 1.6                                 |

| 9    | k <sub>i</sub> (Temperature Coefficient)                   | 0.065 A/°C                          |

| 10   | S(Solar radiation)                                         | $1000 \text{ W/m}^2$                |

| 11   | E <sub>g</sub> (Forbidden energy gap)                      | 1.1 eV                              |

| 12   | N <sub>s</sub> (number of solar cells connected in series) | 216                                 |

| 13   | $N_p$ (number of solar cells connected in parallel)        | 1                                   |

| 14   | R <sub>s</sub> (Source resistance)                         | 0.0002 ohms                         |

| 15   | R <sub>sh</sub> (shunt resistance)                         | 100000 ohms                         |

| 16   | V <sub>pv</sub> (Ramp Maximum Voltage)                     | 70V                                 |

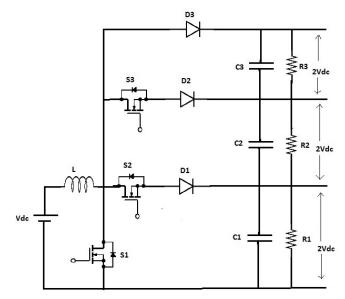

#### B. Proposed SITO DC-DC Boost Converter

Usually in conventional methods, the output from the solar panel has to be boosted up by using a boost converter and the boosted voltage is fed to the MLI where splitting capacitors are used to split up the voltage depending on the number of output voltage levels and the scheme of the DC source (asymmetric or symmetric scheme). The usage of capacitors is given by,

Number of capacitors,

$$C = 2^n + 1$$

(5)

where n=number of output voltage levels of MLI.

Due to this splitting capacitors, voltage balancing problems are occurring during the splitting of voltages. Thereby, it affects the THD value of the output voltage and it creates voltage stress on the switches.

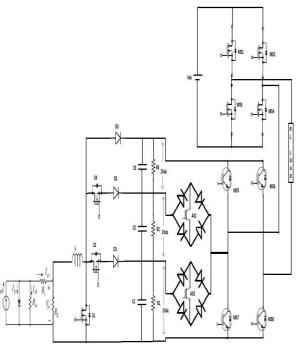

In order to rectify this problem, SITO DC-DC converter is proposed which is shown in fig.3 in this paper. By using SITO DC-DC boost converter it is able to generate three output levels which may be an asymmetric or symmetric voltage sources. In this paper, the output voltage of SITO DC-DC boost converter is (94V X 3) = 282V (i.e. 94V is a single output voltage).Boosting and splitting of voltage levels is done in this SITO DC –DC boost converter. Thereby, the THD value and voltage stress on the switching devices are reduced.

Fig 3. Circuit diagram of SITO DC-DC boost converter

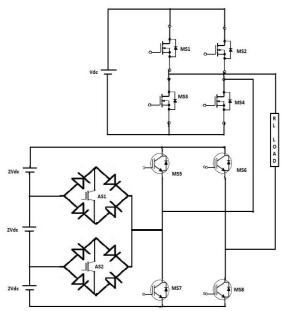

## C. Proposed Hybrid 15level Cascaded MLI

Number In conventional method of symmetric voltage source based MLI, 16 switching devices are needed to generate 15 level output. In this paper, a new hybrid Cascaded MLI is developed with reduced number of switching devices which is capable of generating 15 output voltage levels.

$$P = \left\lceil \left( \frac{n-11}{4} \right) + 9 \right\rceil \tag{6}$$

where n= number of output voltage levels of MLI.

To generate 15 levels of output only 10 switching devices and to generate 19 levels of output, only 11 switching devices are required.

Fig.4 shows the circuit diagram of proposed hybrid 15 level cascaded MLI. In which, there are two inverters are in cascaded connection namely upper inverter and lower inverter. Upper inverter is given with a voltage source with magnitude of  $V_{dc}$  (47V) and lower inverter is given with 3 voltage sources with magnitude of  $2V_{dc}$  (94V) each (i.e total  $6V_{dc}$ ). The upper inverter is able to produce two levels ( $\pm V_{dc}$ ) and lower inverter produces 7 levels ( $\pm 2V_{dc}$ ,  $\pm 4V_{dc}$ ,  $\pm 6V_{dc}$ , 0). In cascaded form, the cascaded MLI produces 15 levels of output voltage with maximum voltage of 329V which is given in the equ. 9..

Number of levels given by the equation in lower inverter,

$$n_{low} = (2a_{low} + 1) \tag{7}$$

Number of levels given by the equation in upper inverter,

$$n_{upper} = \left(a_{upper} + 1\right) \tag{8}$$

where

a<sub>low</sub>= Number of DC sources used in lower inverter a<sub>upper</sub>= Number of DC sources used in upper inverter

$n_{low}\!\!=\!$  Number of levels produced by lower inverter  $n_{upper}\!\!=\!$  Number of levels produced by lower inverter

Fig 4. Circuit diagram of proposed hybrid 15level cascaded MLI converter

And maximum voltage of the cascaded MLI is

$$V_{o \max} = \left[ \left( a_{upper} * V_{dc} \right) + \left( a_{low} * 2V_{dc} \right) \right]$$

(9)

For the proposed system in addition with SITO DC-DC boost converter, which is shown in fig.5, the number of power switching devices is given by

$$P = \left[ \left( \frac{n-11}{4} + 9 \right) + Q \right] \tag{10}$$

where Q= Number of switching devices in SITO converter

Fig 5.Circuit diagram of proposed MLI with SITO DC-DC boost converter

#### 3. Proposed Pulse Width Modulation

A new hybrid pulse width modulation technique is proposed for this topology. Hybrid PWM technique is a combination of modified sinusoidal pulse width modulation and stair case pulse width modulation. Modified sinusoidal PWM is proposed for upper inverter to produce the output voltage at high frequency and stair case PWM is proposed for lower inverter to produce the output voltage at lower frequency. For modified sinusoidal PWM, the reference waveform is

$$V_{ref} = A\sin wt \tag{11}$$

where A is peak value of reference waveform which is given by A = (2Q+1)

Unified pulses

$$Z_{1} = 1 \text{ if } V_{ref} > 0 \tag{12}$$

$$Z_2 = 1 \text{ if } V_{ref} < 0 \tag{13}$$

$$V_{u,\exp} = \left[ round \left( \frac{V_{ref}}{0.4} \right) * 0.4 * Z_1 \right] + \left[ round \left( \frac{V_{ref}}{0.4} \right) * 0.4 * (-Z_1) \right]$$

(14)

Modified reference waveform for upper inverter is

$$V_{up,ref} = \left(V_{ref} - V_{u,\text{exp}}\right) \tag{15}$$

By comparing modified sinusoidal reference waveform with triangular carrier waveform, switching pulses for upper inverter is to be determined which is given in table II.

For staircase PWM,

Three staircase reference waveforms  $R_1$ ,  $R_2$  and  $R_3$  are generated along with  $Z_1$ ,  $Z_2$  where

Table 2 Switching sequence of upper inverter

| Output<br>Voltage Level | $MS_1$ | $MS_2$ | $MS_3$ | $MS_4$ |

|-------------------------|--------|--------|--------|--------|

| $V_{dc}$                | 1      | 0      | 0      | 1      |

| 0                       | 0      | 0      | 0      | 0      |

| -V <sub>dc</sub>        | 0      | 1      | 1      | 0      |

$$Z_1 = 1 \text{ if } V_{raf} > 0 \tag{16}$$

$$Z_2 = 1 \text{ if } V_{ref} < 0 \tag{17}$$

The switching pulses, shown in table III, for all the switching devices including auxiliary switching devices are generated by comparing  $R_1, R_2, R_3$  and  $Z_1, Z_2$  which is given by the equations,

$$S_1 = \left(\overline{R_1}(or)R_3\right) * Z_1 \tag{18}$$

$$S_2 = \left\lceil \left( R_1 * Z_2 \right) (or) \left( \overline{R_1} * Z_1 \right) \right\rceil \tag{19}$$

$$S_3 = \left(\overline{R_1}(or)R_3\right) * Z_2 \tag{20}$$

$$S_4 = \left\lceil \left( R_1 * Z_1 \right) (or) \left( \overline{R_1} * Z_2 \right) \right\rceil \tag{21}$$

$$S_{5} = \left[ \left( R_{1}(xor)R_{2} \right) * Z_{2} \right] (or) \left[ \left( R_{2}(xor)R_{3} \right) * Z_{1} \right]$$

(22)

$$S_6 = \left[ \left( R_1(xor) R_2 \right) * Z_1 \right] (or) \left[ \left( R_2(xor) R_3 \right) * Z_2 \right]$$

(23)

Table 3 Switching sequence of lower inverter

| Output<br>Voltage<br>Level | MS <sub>5</sub> | MS <sub>6</sub> | MS <sub>7</sub> | MS <sub>8</sub> | $AS_1$ | AS <sub>2</sub> |

|----------------------------|-----------------|-----------------|-----------------|-----------------|--------|-----------------|

| $2 V_{dc}$                 | 0               | 0               | 0               | 1               | 0      | 1               |

| 4 V <sub>dc</sub>          | 1               | 0               | 0               | 1               | 1      | 1               |

| 6 V <sub>dc</sub>          | 1               | 0               | 0               | 1               | 0      | 0               |

| 0                          | 0               | 0               | 0               | 0               | 0      | 0               |

| -2 V <sub>dc</sub>         | 0               | 1               | 0               | 0               | 1      | 0               |

| -4 V <sub>dc</sub>         | 0               | 1               | 0               | 0               | 0      | 1               |

| -6 V <sub>dc</sub>         | 0               | 1               | 1               | 0               | 0      | 0               |

#### 4. Voltage Rating of the devices

The rating of the switching devices should be selected prudently in the proposed inverter, because of the dissimilarities in the voltage rating of each device. Only one auxiliary switch is required in the proposed topology of 11-level inverter. In this case, the voltage of auxiliary switch will bounce between 0 and 2V<sub>dc</sub> because the total voltage  $4V_{\text{dc}}$  is alienated into two by splitting capacitors (i.e) 2V<sub>dc</sub> each. Therefore, capacitor voltage of  $2V_{dc}$  has to be blocked by the auxiliary switches. Likewise, two auxiliary switches are required in the proposed topology of 15-level inverter. The total voltage 6V<sub>dc</sub> is alienated into three by three splitting capacitors (i.e) 2V<sub>dc</sub> across each. Hence, the voltage of two auxiliary switches will bounce between 0 and 4Vdc. Further, three auxiliary switches are required in 19-level inverter. The voltages of first and last auxiliary switch will bounce between 0 and 6V<sub>dc</sub> and the voltage of middle auxiliary switch will bounce between 0 and 4V<sub>dc</sub>. Similarly, for other levels of inverters of this topology, the voltage of first and last auxiliary switch voltage bounces between 0 and  $((n-1)mV_{dc}/n)$ , whereas the voltage of other auxiliary switch bounces between 0 and  $((n-2)mV_{dc}/n)$ ,  $((n-3)mV_{dc}/n)$ ...and so on and where n is the number of splitting capacitors and  $mV_{dc}$  is total voltage applied for the lower inverter.

# 5. Simulation and hardware results

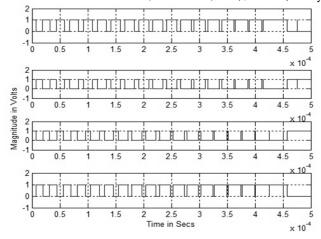

Fig.6 shows the generation of pulses for upper inverter switching devices which is done by comparing the modified sinusoidal waveform with triangular

carrier waveform at (400 kHz) high frequency.

Fig 6. Gate pulse of upper inverter

Fig.7 shows the generation of pulses for lower inverter switching devices which is done by comparing the using staircase PWM with triangular carrier waveform at (50 Hz) low frequency [29].

Fig 7. Gate pulse of lower inverter

Fig. 8 shows the 15level output voltage waveform of proposed MLI with voltage splitting capacitors where voltage mismatching has occurred due to voltage balancing problem.

Fig 8. 15level output voltage waveform of proposed MLI with splitting capacitors

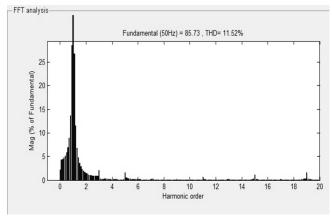

Fig. 9 shows the THD value of 15 level output voltage waveform of conventional MLI.

Fig 9. THD plot of output voltage of 15level proposed MLI with splitting capacitors

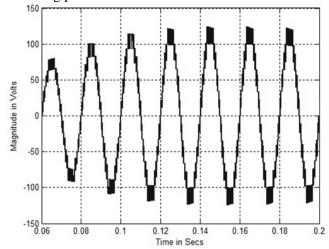

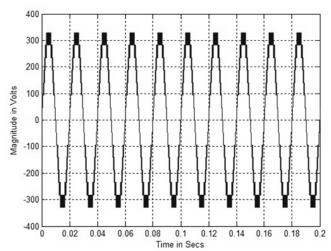

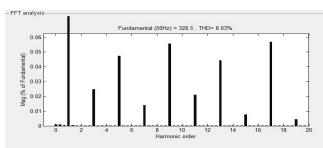

Fig. 10 shows the 15level output voltage waveform of proposed MLI where voltage balancing problem has overcome and in fig. 11, it is observed that the THD value of output voltage waveform of proposed MLI has been reduced when compared with conventional MLI.

Fig 10. Output voltage waveform of 15level MLI with SITO DC-DC boost converter

Fig. 11 THD plot of output voltage of 15level MLI with SITO DC-DC boost converter

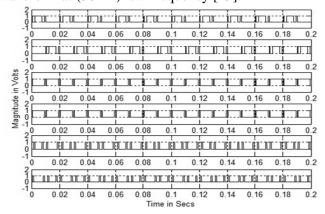

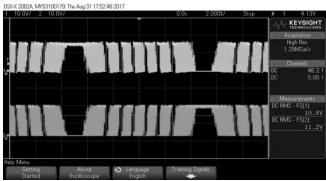

Fig. 12.a. and 12.b. shows the hardware output of switching pulses for upper inverter.

Fig 12.a. Hardware output of switching pulses for switches MS1 and MS3 of upper inverter

Fig 12.b. Hardware output of switching pulses for switches MS2 and MS4 of upper inverter

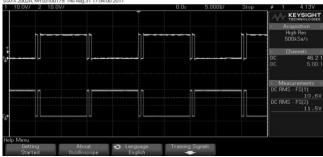

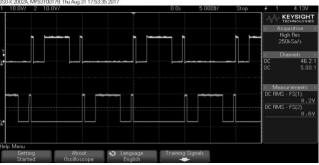

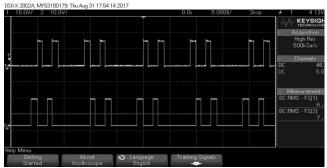

Fig. 13.a., 13.b. and 13.c. shows the hardware output of switching pulses for lower inverter.

Fig 13.a. Hardware output of switching pulses for switches MS5 and MS7 of lower inverter

Fig 13.b. Hardware output of switching pulses for switches MS6 and MS8 of lower inverter

Figure 13.c. Hardware output of switching pulses for switches AS1 and AS2 of lower inverter

Figure 14.a. DC output voltage of boost converter given for upper inverter

Output1 from SITO converter

Output2 from SITO converter

Output3 from SITO converter

Figure 14.b. DC output voltage of SITO boost converter given for lower inverter

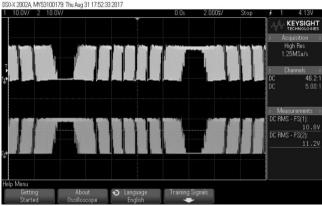

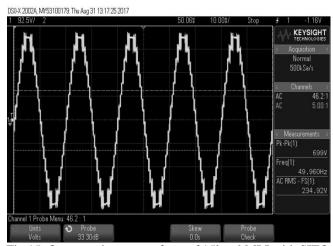

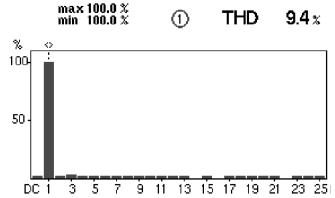

Fig. 14.a, 14.b show the hardware output voltage of boost converter which is given as input for upper inverter and lower inverter respectively. Fig. 15, 16 shows the 15level output voltage waveform of proposed MLI with SITO boost converter that is observed from Digital storage oscilloscope and THD value of output voltage waveform respectively.

Fig 15. Output voltage waveform of 15level MLI with SITO DC-DC boost converter

Fig 16. Output voltage waveform of 15level MLI with SITO DC-DC boost converter

Fig. 17. Hardware implementation of 15level MLI with single input triple output DC-DC boost converter

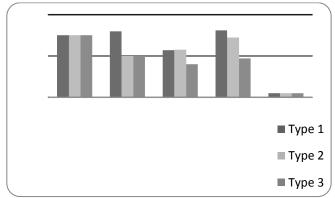

Comparison of conventional MLI [6] and proposed topology of MLI is given in the table IV and fig.18.

Table 4 Comparison of number of levels, number of switching devices, THD value and No. of DC Sources

| Method | Leve<br>1 | No of<br>Switch | THD<br>in % |              | DC<br>Sour |

|--------|-----------|-----------------|-------------|--------------|------------|

|        |           | Used            | Simula tion | Hard<br>ware | ces        |

| Type 1 | 15        | 16              | 11.4        | 16.2         | 1          |

| Type 2 | 15        | 10              | 11.52       | 14.5         | 1          |

| Type 3 | 15        | 10              | 8.02        | 9.4          | 1          |

In table 4.

Type 1: Conventional type MLI with single DC source and splitting capacitors

Type 2: Proposed MLI with single DC source and splitting capacitors

Type 2: Proposed MLI with single input triple output DC-DC boost converter

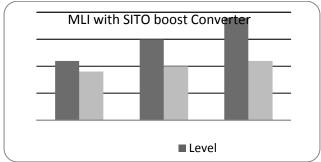

Table 5 Comparison of Different levels of MLI constructed by using the proposed topology

| S.No | Method                              | Level | Number of<br>Switching<br>Devices Used |

|------|-------------------------------------|-------|----------------------------------------|

| 1    | MLI with<br>SITO boost<br>Converter | 11    | 9                                      |

| 2    |                                     | 15    | 10                                     |

| 3    |                                     | 19    | 11                                     |

Fig 18. Graphical comparison of 15level conventional MLI with proposed topology

Fig 19. Graphical comparison of different levels of proposed

MLI topologies

#### 6. Results and Discussions

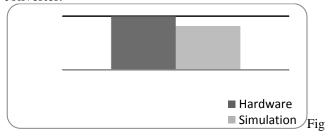

The results of the proposed MLI topology are compared with the conventional type of MLI topology [1], [2], [3], [5], [6], [11] and it is exhibited in the above sections. From the comparison, it is concluded that the proposed type of MLI with SITO boost converter has been found to be more efficient with low value of THD values of output voltage, free from the voltage balancing problems which cause severe troubles in the case of high voltage applications and the number of power semiconductor switching devices required for higher voltage level generations is also reduced. It is concluded that the performance of combined proposed MLI with SITO boost converter is better than the combined proposed MLI with single DC source and splitting capacitors. During Hardware implementation of the proposed SITO boost converter, a small deviation is found in the output voltage of SITO boost converter when compared with simulation output which is shown in the table 6 and fig. 20.

Table 6 Comparison of output voltage of SITO boost converter between hardware and simulation outputs.

| converter between hardware and simulation outputs. |                                                           |  |  |  |

|----------------------------------------------------|-----------------------------------------------------------|--|--|--|

| Type                                               | MLI with SITO boost Converter<br>Output Voltage(in Volts) |  |  |  |

| Hardware                                           | *99+101+101=301V                                          |  |  |  |

| Simulation                                         | *94+94+94=282V                                            |  |  |  |

\*which represents the triple output voltage of SITO converter.

Graphical comparison of hardware and simulation output voltages of SITO converter

#### 7. Conclusion

The cascaded 15 level hybrid SITO DC-DC boost converter is proposed with reduced number of switching devices and generates output level with low THD value when compared with conventional MLI which is shown in the table IV. The comparison table for different level of MLI which is constructed by

using the proposed topology is shown in table V and fig.19. Proposed SITO DC –DC boost converter eliminates the voltage balancing problem which is arising in conversional MLI and this is the best boost converter for solar PV application. Thus, it can be used for medium and high power applications.

#### 8. References

- Junfeng Liu, Jialei Wu, Jun Zeng, and HuafangGuo, "A Novel Nine-Level Inverter Employing One Voltage Source and Reduced Components as High-Frequency AC Power Source", IEEE Transactions on Power Electronics, Vol. 32, No. 4, April 2017.

- RasoulShalchiAlishah, SeyedHosseinHosseini, EbrahimBabaei, and MehranSabahi, "Optimal Design of New Cascaded Switch-Ladder Multilevel Inverter Structure", IEEE Transactions on Industrial Electronics, Vol. 64, No. 3, March 2017.

- 3. Amir Taghvaie, JafarAdabi, and Mohammad Rezanejad, "Circuit Topology and Operation of a Step-Up Multilevel Inverter With a Single DC Source", IEEE Transactions on Industrial Electronics, Vol. 63, No. 11, November 2016.

- 4. Amin Gholizad and MurtazaFarsadi, "A Novel State-of-Charge Balancing Method Using Improved Staircase Modulation of Multilevel Inverters," IEEE Transactions on Industrial Electronics, Vol. 63, No. 10, Oct. 2016.

- 5. Boora A.A., Nami A., Zare F., Ghosh A., Blaabjerg "Voltage sharing converter to supply single phase asymmetrical four level diode clamped inverter with high power factor loads" in IEEE Trans. On Power Electron., 25, (10), 2012, pp. 2507–2520.

- 6. Boora A.A., Nami A., Zare F., Ghosh, A., Blaabjerg F.: "A hybrid cascaded converter topology with series-connected symmetrical and asymmetrical diode clamped H bridge cells" in IEEE Trans. Power Electron. 26, (1), 2012, pp. 51–65.

- 7. Jie Zhang, YunpingZou, Xian Zhang and Kaiding "Study on a Modified cascade inverter with hybrid modulation." inProceedings of the 4th IEEE International Conference on Power Electronics and Drive Systems, vol.1, Oct.2001, pp 379 383.

- Drive Systems, vol.1, Oct.2001, pp 379 383.

8. Hinago Y., Koizumi H. "A single-phase multilevel inverter using switched series/parallel DC voltage sources" in IEEE Trans. Ind. Electron., 57, (8), 2010, pp. 2643–2650.

- 9. Amorndechaphon D., Premrudeepreechacharn S. and Higuchi K.: "Modified Grid-Connected Current Source Inverter for Multi-string PV System." in Power Electronics, IEEE Trans. on vol.56, no.11, 2011, pp.4381-4388.

- Nasrudin A. Rahim and JeyrajSelvaraj "Multistring Five-Level Inverter With Novel PWM Control Scheme for PV Application." In IEEE Trans. Ind. Electronics, vol. 57, no. 6, June 2010, pp. 2111-2123.

- 11. Nasrudin A. Rahim, KrismadinataChaniago and JeyrajSelvaraj "Single-Phase Seven-Level Grid-Connected Inverter for Photovoltaic System" in IEEE Trans. Ind. Electronics, vol.58, no. 6, June 2011, pp. 2435-2443.

- 12. Rahim N.A., Selvaraj "Multistring five-level inverter with novel PWM control scheme for PV application" in IEEE Trans. Ind. Electron., 57, (6), 2010, pp. 2111–2123.

- 13. Shimizu T., Hashimoto O., "A novel high-performance utility-interactive photovoltaic inverter system" in Power Electronics, IEEE Transactions on , vol.18, no.2, Mar 2003 , pp. 704-711.

- 14. Tolbert, Leon M., Fang Z. Peng: "Multilevel converters as a utility interface for renewable energy systems" in

- Power Engineering Society Summer Meeting, 2000. IEEE, vol. 2, pp. 1271-1274.

- 15. HamedNademi, Rolando Burgos., "A New Circuit Performance of Modular Multilevel Inverter Suitable for Photovoltaic Conversion Plants" in IEEE Journal of Emerging and Selected Topics In Power Electronics, vol. 04, no. 2, June 2016, pp. 393-404.

- Irfan Ahmed, Vijay B. Borghate, AmarendraMatsa, Prafullachandra M. Meshram, HiralalMurlidharSuryawanshi, Madhuri A. Chaudhari., "Simplified Space Vector Modulation Techniques for MultilevelInverters", in IEEE Transactions on Power Electronics, vol. 31, No. 12, December 2016, pp. 8483-8499.

- 17. EmadSamadaei, SayyedAsgharGholamian, AbdolrezaSheikholeslami, JafarAdabi, "An Envelope Type (E-Type) Module: Asymmetric Multilevel Inverters With Reduced Components" in IEEE Transactions on Industrial Electronics, vol. 63, no. 11, November 2016, pp. 7148-7156.

- 18. Jalal Amini, Abbas HooshmandViki, Ahmad Radan, MehrdadMoallem, "A General Control Method for Multilevel Converters Based on Knapsack Problem"in IEEE Transactions on Power Electronics, vol. 32, no. 1, January 2017, pp. 2-10.

- 19. Viju Nair R, Arun Rahul S, R. SudharshanKaarthik, AbhijitKshirsagar, K. Gopakumar, "Generation of Higher Number of Voltage Levels by Stacking Inverters of Lower Multilevel Structures With Low Voltage Devices for Drives" in IEEE Transactions on Power Electronics, vol. 32, no. 1, January 2017, pp. 52-59.

- ElyasZamiri, NaserVosoughi, SeyedHosseinHosseini, Reza Barzegarkhoo, MehranSabahi, "A New Cascaded Switched-Capacitor Multilevel Inverter Based on Improved Series-Parallel Conversion With Less Number of Components" in IEEE Transactions on Industrial Electronics, vol. 63, no. 6, June 2016, pp. 3582-3594.

- C. Bharatiraja, S. Jeevananthan, J.L. Munda, and R. Latha, "Improved SVPWM vector selection approaches in OVM region to reduce common-mode voltage for three-level neutral point clamped inverter," International Journal of Electrical Power & Energy Systems/ Elsevier, vol. 79, no. 1, pp. 285–297, Oct. 2016.

- 22. Raghavendra Reddy Karasani, Vijay BhanujiBorghate, Prafullachandra M. Meshram, HiralalMurlidharSuryawanshi, SidharthSabyasachi, "A Three-Phase Hybrid Cascaded Modular Multilevel Inverter for Renewable Energy Environment" in IEEE Transactions on Power Electronics, vol. 32, no. 2, February 2017, pp. 1070- 1087.

- Ahmed Salem, Emad M. Ahmed, Mohamed Orabi, Mahrous Ahmed, "Study and Analysis of New Three-Phase Modular Multilevel Inverter"in IEEE Transactions on Industrial Electronics, vol. 63, no. 12, December 2016, pp. 7804-7813.

- Kehu Yang , Qi Zhang, Jianjun Zhang, Ruyi Yuan, Qiang Guan, Wensheng Yu, Jin Wang, "Unified Selective Harmonic Elimination for Multilevel Converters" in IEEE Transactions on Power Electronics, vol. 32, no. 2, February 2017, pp. 1579-1590.

- 25. Seok-Min Kim, June-Seok Lee, Kyo-Beum Lee, "A Modified Level-Shifted PWM Strategy for Fault-Tolerant Cascaded Multilevel Inverters With Improved Power Distribution", in IEEE Transactions on Industrial Electronics, vol. 63, no. 11, November 2016, pp. 7264-7274.

- 26. VenuSonti, Sachin Jain, Subhashish Bhattacharya, "Analysis of the Modulation Strategy for the Minimization of the Leakage Current in the PV Grid-

- Connected Cascaded Multilevel Inverter", in IEEETransactions on Power Electronics, vol. 32, no. 2,

- February 2017, pp. 1156-1169.

- 27. MahranQuraan, PietroTricoli, Salvatore D'Arco, Luigi Piegari, "Efficiency Assessment of Modular Multilevel Converters for Battery Electric Vehicles", in IEEE Transactions on Power Electronics, vol. 32, no. 3, March 2017, pp. 2041- 2051.

- 28. Mohamed Trabelsi, SertacBayhan, Khalid Ahmed Ghazi, Haitham Abu-Rub, Lazhar Ben-Brahim, "Finite-Control-Set Model Predictive Control for Grid-Connected Packed-U-Cells Multilevel Inverter", in IEEE Transactions on Industrial Electronics, vol. 63, no. 11, November 2016, pp. 7286-7295.

- 29. C. Bharatiraja, R. Selvaraj, T. R. Chelliah, J. L. Munda, M. Tariq, and A. I. Maswood, "Design and Implementation of Fourth Arm for Elimination of Bearing Current in NPC-MLI-Fed Induction Motor Drive," IEEE Transactions on Industry Applications, vol. 54, no. 1, pp. 745–754, Jan. 2018

- P. Anbarasan,S. Ramkumar and C.Bharatiraja,"A Comprehensive Analysis of Carrier Shifting Algorithms for Diode-Clamped MLI Based Drive", in Journal of Electrical Engineering, Vol.17, No.2, 2017, pp.52-61, 2017.

- 31. C. Bharatiraja, S. Jeevananthan, and J. L. Munda, "A Timing Correction Algorithm-Based Extended SVM for Three-Level Neutral-Point-Clamped MLI in Over Modulation Zone," IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 6, no. 1, pp. 233–245, Mar. 2018