# THE ENERGY EFFICIENT INDUCTION MOTOR DRIVE USING SEVEN LEVEL MULTILEVEL INVERTER

R.Chandralekha<sup>1</sup> D.Nivea<sup>2</sup> T.Geethapriya<sup>3</sup>

Assistant Professor Assistant Professor Assistant Professor lekhroseanu@vahoo.com er.nivea@gmail.com geethapriva86@gmail.com

Department of Electrical and Electronics Engineering Vel tech Multitech, Chennai,

#### Abstract

The main objective of this project is to control the speed of an induction motor by using seven level diode clamped multilevel inverter. To obtain high quality sinusoidal output voltage with reduced harmonics The proposed Scheme for diode clamped multilevel inverter is multicarrier SPWM control. An open loop speed control can be achieved by using V/f method. This method can be implemented by changing the supply voltage and frequency applied to the three phase induction motor at constant ratio. The proposed system is an effective replacement for the conventional method which has high switching losses, as a result a poor drive performance. Here the new simulink model has been designed to have better performance. The simulation result portrays the effective control in the motor speed and an enhanced drive performance through reduction in total harmonic distortion (THD). The effectiveness of the system is verified through simulation using MATLAB Simulink package.

**Key words:** SPWM, Multilevel Inverter, Total harmonic Distortion, Induction Motor Drive, FACTS, Traction Drive system

#### 1. INTRODUCTION

Numerous industrial applications have begun to require higher power apparatus in recent years. Some medium voltage motor drives and utility applications require medium voltage and megawatt power level. For a medium voltage grid, it is troublesome to connect only one power semiconductor switch directly. As a result, a multilevel power converter structure has been introduced as an alternative in high power and medium voltage situations.

A multilevel converter not only achieves high power ratings, but also enables the use of renewable energy sources. Renewable energy sources such as photovoltaic, wind, and fuel cells can be easily interfaced to a multilevel converter system for a high power application. The concept of multilevel converters has been introduced since 1975. The term multilevel began with the three-level converter. Subsequently, several multilevel converter topologies have been developed. However, the elementary concept of a multilevel converter to achieve higher power is to use a series of power semiconductor switches with several lower voltage dc sources to perform the power conversion by synthesizing a staircase voltage waveform. Capacitors, batteries, and renewable energy voltage sources can be used as the multiple dc voltage sources. The commutation of the power switches aggregate these multiple dc sources in order to achieve high voltage at the output; however, the rated voltage of the power semiconductor switches depends only upon the rating of the dc voltage sources to which they are connected. A multilevel converter has several advantages over a conventional two-level converter that uses high switching frequency pulse width modulation (PWM). The attractive features of a multilevel converter can be briefly summarized as follows. Staircase waveform quality: multilevel converters not only can generate the output voltages with very low distortion, but also reduce the dv/dt stresses; therefore electromagnetic compatibility (EMC) problems can reduced. Common-mode (CM) Multilevel converters produce smaller CM voltage; therefore, the stress in the bearings of a motor connected to a multilevel motor drive can be reduced. Furthermore, CM voltage can be eliminated by using advanced modulation strategies such as that proposed in.

- Input current: Multilevel converters can draw input current with low distortion.

- Switching frequency: Multilevel converters can at both fundamental switching frequency and high switching frequency PWM.

It should be noted that lower switching frequency usually means lower switching loss and higher efficiency. Unfortunately, multilevel converters do disadvantages. have some One particular disadvantage is the greater number of power semiconductor switches needed. Although lower voltage rated switches can be utilized in a multilevel converter, each switch requires a related gate drive circuit. This may cause the overall system to be more expensive and complex. Plentiful multilevel converter topologies have been proposed during the last two decades. Contemporary research has engaged novel converter topologies and unique modulation schemes. Moreover, three different major multilevel converter structures have been reported in the literature: cascaded H-bridges converter with separate dc sources, diode clamped (neutral-clamped), and flying capacitors (capacitor clamped).

Moreover, abundant modulation techniques and control paradigms have been developed for multilevel converters such as sinusoidal pulse width modulation (SPWM), selective harmonic elimination (SHE-PWM), space vector modulation (SVM), and others. In addition, many multilevel converter applications focus on industrial medium-voltage motor drives, utility interface for renewable energy systems, flexible AC transmission system (FACTS), and traction drive systems.

This chapter reviews state of the art of multilevel power converter technology. Fundamental multilevel converter structures and modulation paradigms are discussed including the pros and cons of each technique. Particular concentration is addressed in modern and more practical industrial applications of multilevel converters. A procedure for calculating the required ratings for the active switches, clamping diodes, and dc link capacitors including a design example are described. Finally, the possible future developments of multilevel converter technology are noted.

# 2.EXISTING SYSTEM

Multi level inverters are so far developed for various fields in power systems like in FACTS, in developing STATCOM etc. Now this multi level inverter is developed up to six levels for using in FACTS, STATCOM and traction drive system. This multi level inverter is used in interfacing with renewable energy for improving power utility.

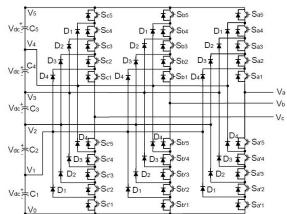

Experimental results for four-, five-, and sixlevel diode-clamped converters for such uses as static var compensation, variable speed motor drives, and high-voltage system interconnections. A three-phase six-level diode-clamped inverter is shown in Figure 1.1.

Each of the three phases of the inverter shares a common dc bus, which has been subdivided by five capacitors into six levels. The voltage across each capacitor is  $V_{\rm dc}$ , and the voltage stress across each switching device is limited to  $V_{\rm dc}$  through the clamping diodes. Table 1.1 lists the output voltage levels possible for one phase of the inverter with the negative dc rail voltage  $V_0$  as a reference. State condition 1 means the switch is on, and 0 means the switch is off.

Each phase has five complementary switch pairs such that turning on one of the switches of the pair requires that the other complementary switch be turned off. The complementary switch pairs for phase leg a are  $(S_{a1}, S_{a'1})$ ,  $(S_{a2}, S_{a'2})$ ,  $(S_{a3}, S_{a'3})$ ,  $(S_{a4}, S_{a'4})$ , and  $(S_{a5}, S_{a'5})$ . Table 1.1 also shows that in a diode-clamped inverter, the switches that are on for a particular phase leg is always adjacent and in series. For a six-level inverter, a set of five switches is on at any given time.

**Fig 2.1** Three-phase six-level structure of a diodeclamped inverter.

| Voltage Va0  | Switch State |          |          |          |          |           |      |           |           |      |

|--------------|--------------|----------|----------|----------|----------|-----------|------|-----------|-----------|------|

|              | Sas          | $S_{a4}$ | $S_{a3}$ | $S_{a2}$ | $S_{al}$ | $S_{a'5}$ | Sa'4 | $S_{a'3}$ | $S_{a'2}$ | Sail |

| $V_5 = 5Vdc$ | 1            | 1        | 1        | 1        | 1        | 0         | 0    | 0         | 0         | 0    |

| $V_4 = 4Vdc$ | 0            | 1        | 1        | 1        | 1        | 1         | 0    | 0         | 0         | 0    |

| $V_3 = 3Vdc$ | 0            | 0        | 1        | 1        | 1        | 1         | 1    | 0         | 0         | 0    |

| $V_2 = 2Vdc$ | 0            | 0        | 0        | 1        | 1        | 1         | 1    | 1         | 0         | 0    |

| $V_1 = Vdc$  | 0            | 0        | 0        | 0        | 1        | 1         | 1    | 1         | 1         | 0    |

| $V_0 = 0$    | 0            | 0        | 0        | 0        | 0        | 1         | 1    | 1         | 1         | 1    |

**Table 2.1** Diode-clamped six-level inverter voltage levels and corresponding switch states.

### 3. PROPOSED SYSTEM

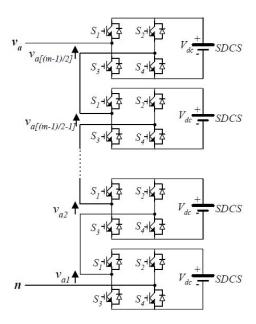

Induction motor drive is developed by using seven level multi level inverter for energy saving in variable torque load. Seven level multi level inverter is designed by using diode clamping method. This diode clamping method requires less number of sources when compared to other techniques.

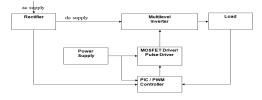

There are three techniques to develop the multilevel inverters namely H-bridge with separate dc sources, diode clamping (neutral point), flying capacitor technique. Among this economically diode clamping and diode clamping is preferable. Flying capacitor technique makes the circuit and its calculation for capacitor complex. Hence diode clamping technique is chosen. In this diode clamping technique, capacitor and switches are required as per ratings which are further explained. The block diagram is as follows:

Fig. 3.1 Block diagram of the proposed system

### 4. MODULES INVOLVED

The modules involved in the development of induction motor drive by using seven level multi level inverter are as follows:

- Phase controlled rectifier

- Seven level multilevel inverter

- Gate driver

- V/F control strategy

- PIC controller

- Load(Induction motor)

## 4.1 Phase controlled rectifier:

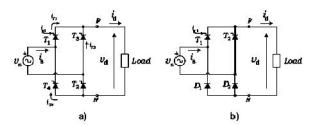

Phase controlled rectifier is used to convert ac supply to dc supply in controlled manner. For this single phase full wave controlled rectifier is used. This rectifier contains four thyristers connected two thyristers in series per leg. Hence rectifier contains two legs. the following figure shows the diagrammatic representation of phase controlled rectifier.

**Fig4. 1** single phase bridge rectifier (a)Fully controlled (b)semi controlled

In a semi-controlled rectifier, control is affected only for positive output voltage, and no control is possible when its output voltage tends to become negative since it is clamped at zero volts. As shown in Fig. (4.2), thyristor T1can be fired into the ON state at any time provided that voltage vT1> 0. The firing pulses are delayed by an angle a with respect to the instant where diodes would conduct. Thruster T1 remains in the ON state until the load current tries to go to a negative value. Thruster T2 is fired into the ON state when vT2> 0, which corresponds in Fig. (4.2) to the condition at which v2> 0. The mean value of the load voltage with resistive load is given by:

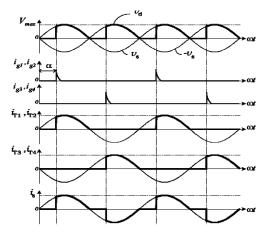

**Fig. 4.2**: Single phase semi-controlled rectifiers waveform

Figure (4.3) shows the voltage and current waveforms of the fully controlled bridge rectifier for a resistive load. Thyristors T1 and T2 must be fired simultaneously during the positive half-wave of the source voltage Vs to allow conduction of current. Alternatively, thyristors T3 and T4 must be fired simultaneously during the negative half wave of the source voltage. To ensure simultaneous firing, thyristors T1 and T2 use the same firing signal.

**Fig.(4.3)** Waveforms of a fully controlled bridge rectifier with resistive load.

Figure (4.4) presents the behavior of the fully controlled rectifier with resistive-inductive load (with  $L\rightarrow\infty$ ). The high-load inductance generates a perfectly filtered current and the rectifier behaves like a current source. With continuous load current, thyristors T1 and T2 remain in the on-state beyond the positive half-wave of the source voltage Vs. For this reason, the load voltage Vdc can have a negative instantaneous value. The firing of thyristors T3 and T4 has two effects:

- a. They turn off thyristors T1 and T2; and

- b. After the commutation, they conduct the load current.

This is the main reason why this type of converter is called a "naturally commutated" or "line commutated" rectifier. The supply current  $i_s$  has the square waveform shown in Fig.(4) for continuous conduction. In this case, the average load voltage is given by:

$$V_{di\alpha} = \frac{1}{\pi} \int_{\alpha}^{\pi+\alpha} V_{max} \sin \omega d(\omega t) = \frac{2V_{max}}{\pi} \cos \alpha$$

**Fig.(4.4)**: Waveforms of a fully controlled bridge Rectifier with resistive-inductive load  $(L\rightarrow\infty)$ .

### 4.2 Seven level multi level inverter:

As mentioned before there are three major techniques to design the multilevel inverter. They are

- H-bridge with separate dc source

- Diode clamping(neutral point technique)

- Flying capacitor technique.

Among these techniques, economically diode clamping and flying capacitor technique is preferable. But flying capacitor technique makes the circuit and the calculation complex. Hence the diode clamping technique is chosen.

## 4.2.1 H-bridge technique:

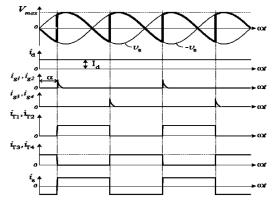

A single-phase structure of an m-level cascaded inverter is illustrated in Figure 31.1. Each separate dc source (SDCS) is connected to a single-phase full-bridge, or H-bridge, inverter. Each inverter level can generate three different voltage outputs,  $+V_{\rm dc}$ , 0, and  $-V_{\rm dc}$  by connecting the dc source to the ac output by different combinations of the four switches,  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$ . To obtain  $+V_{\rm dc}$ , switches  $S_1$  and  $S_4$  are turned on, whereas  $-V_{\rm dc}$  can be obtained by turning on switches  $S_2$  and  $S_3$ .

By turning on  $S_1$  and  $S_2$  or  $S_3$  and  $S_4$ , the output voltage is 0. The ac outputs of each of the different full-bridge inverter levels are connected in series such that the synthesized voltage waveform is the sum of the inverter outputs. The number of output phase voltage levels m in a cascade inverter is defined by m = 2s+1, where s is the number of separate dc sources. An example phase voltage waveform for an 11-level cascaded H-bridge inverter with 5 SDCSs and 5 full bridges is shown in Figure 4.5. The phase voltage  $v_{an} = v_{a1} + v_{a2} + v_{a3} + v_{a4} + v_{a5}$ .

For a stepped waveform such as the one depicted in Figure 5 with s steps, the Fourier Transform for this waveform follows:

$V(wt) = (4V_{dc}/\pi)\Sigma[\cos(n\theta_1) + \cos(n\theta_2) + ....]\sin(nwt)/n$

**Fig 4.5** Single-phase structure of a multilevel cascaded H-bridges inverter.

Fig 4.6 Squirrel Cage Induction Motor

The three-phase AC induction motor has a squirrel cage rotor in which aluminum conductors or bars are shorted together at both ends of the rotor by cast aluminum end rings. When three currents flow through the three symmetrically placed windings, a sinusoidally distributed air gap flux generating the rotor current is produced. The interaction of the sinusoidally distributed air gap flux and induced rotor currents produces a torque on the rotor. The mechanical angular velocity of the rotor is lower then the angular velocity of the flux wave by so called slip velocity.

In adjustable speed applications, AC motors are powered by inverters. The inverter converts DC power to AC power at the required frequency and amplitude. The inverter consists of three half-bridge units where the upper and lower switches are controlled complimentarily. As the power device's turn-off time is longer than its turn-on time, some dead-time must be inserted between the turn-off of one transistor of the half-bridge and turn-on of its complementary device. The output voltage is mostly created by a pulse width modulation (PWM) technique. The three-phase voltage waves are shifted 120° to one another and thus a three-phase motor can be supplied.

The stator windings of an AC induction motor are distributed around the stator to produce a roughly sinusoidal distribution. When three-phase AC voltages are applied to the stator windings, a rotating magnetic field is produced.

The rotor of an induction motor also consists of windings or more often a copper squirrel cage embedded within iron laminates. Only the iron laminates are shown. An electric current is induced in the rotor bars which also produce a magnetic field.

The rotating magnetic field of the stator drags the rotor around. The rotor does not quite keep up with the rotating magnetic field of the stator. It falls behind or slips as the field rotates.

In this animation, for every time the magnetic field rotates, the rotor only makes three-fourths of a turn. If you follow one of the bright green or red rotor teeth with the mouse, you will notice it change color as it falls behind the rotating field. The slip has been greatly exaggerated to enable visualization of this concept. A real induction motor only slips a few percent.

An AC motor's synchronous speed, , is the rotation rate of the stator's magnetic field, which is expressed in revolutions per minute as

where f is the motor supply's frequency in Hertz and  $\boldsymbol{P}$  is the number of magnetic poles. That is, for a six-pole three-phase motor with three pole-pairs set 120° apart,  $\boldsymbol{P}$  equals 6 and equals 1,000 RPM and 1,200 RPM respectively for 50 Hz and 60 Hz supply systems.

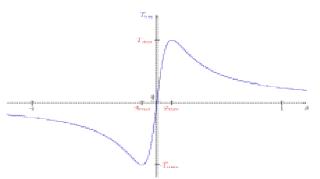

The torque-slip characteristic of the induction motor is as follows:

Fig 4.7 Torque- slip characteristics

## 5. MATLAB CODING AND SIMULATION

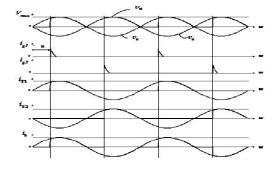

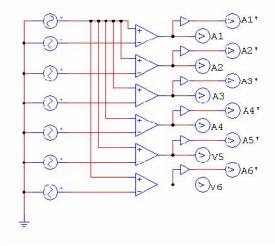

Figure 12. Shows the PWM circuit to generate the gating signals for the multilevel inverter switches. To control a three phase multilevel inverter with an output voltage of seven levels; six carriers are generated and compared at each time to a set of three sinusoidal reference waveforms. One carrier wave above the zero reference and one carrier wave below the reference. These carriers are same in frequency, amplitude and phases; but they are just different in dc offset to occupy contiguous bands. Phase disposition technique has less harmonic distortion on line voltages. Simulated model for entire circuit is shown in Figure 5.1.

Fig 5.1 Multi carrier SPWM simulation circuit

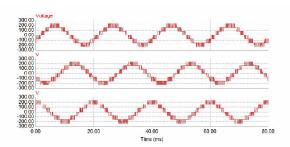

**Fig 5.2** Output Phase Voltage for 50Hz Frequency

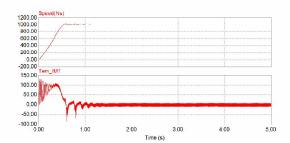

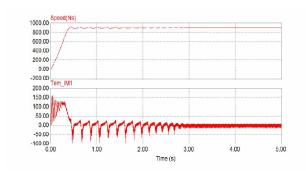

Fig 5.3. N-T Curves for 50Hz Frequency

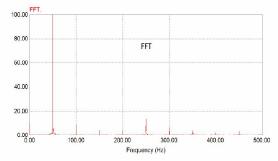

The FFT plot of the output voltage is shown in Figure 15. The plot shows that the harmonic content present in the output voltage is very Low.

**Fig 5.4** FFT for Output Voltage 50HZ. THD=0.7%

The frequency of reference signal determines the inverter output frequency; and its peak amplitude controls the modulation index. The variation in modulation index changes the rms output voltage of the multilevel inverter. By varying the reference signal frequency as well as modulation index, the speed of an induction motor gets controlled.

Fig 5.6 N-T curves for 45Hz frequency

The speed-torque curves conclude that the voltage and frequency applied to the motor gets decreased; then the speed of an induction motor also decreases simultaneously.

## **PROGRAM**

```

#include <16f877a.h>

#use delay (clock=20000000)

#use rs232 (baud=9600,xmit=pin_c6,rcv=pin_c7)

HS.NOWDT.NOPUT.NOLVP.NODEBUG,NOBR

OWNOUT, PROTECT, CPD, NOWRT

static unsigned char

motor=0,data[5],time_count=0,T_flag=0;

unsigned long temperature=0,temp_set=16;

short dis_flag=0,t_dis_flag=0,analog_sc;

float Frq=22, calibration;

#include <lcd drive 2.c>

void uart_intial()

enable_interrupts(global);

void io_intial()

trisa=0xff;

trise=0x00;

trisb=0xf0;

trisc=0x00;

trisd=0x00;

void main()

static unsigned char frequency=28;

static unsigned long voltage=385;

static short flip=0;

io intial();

uart_intial();

lcd_int();

```

```

phase_routine(volt_control,395);

delay ms(5000);

while(true)

if(~portb_7)

delay_ms(100);

motor=0x80;

frequency+=1;

Frq+=0.5;

if(Frq>=55)Frq=55;

if(frequency>=94)frequency=94;

voltage=(unsigned long)(3.50 * Frq

*4.8214);

if(voltage>=928)voltage=928;

phase_routine(volt_control,voltage);

delay ms(600);

printf("%c",frequency|motor);

else if(~portb_6)

delay_ms(100);

motor=0x80:

if(frequency<=28)frequency=28;

else

frequency=1;

Frq=0.5;

if(Frq \le 22)

Frq=22;

voltage=388;

phase routine(volt control, voltage);

delay_ms(600);

frequency=28;

Frq=22;

printf("\%c",0x00);

else

voltage=(unsigned long)(3.50 * Frq

*4.8214):

if(voltage<=388)voltage=388;

phase routine(volt control,voltage);

delay ms(600);

printf("%c",frequency|motor);

}

}

```

### 7. CONCLUSION

In this project a diode clamped multilevel inverter has been presented for drive applications. The multicarrier SPWM technique can be implemented for producing low harmonic contents in the output; hence the high quality output voltage was obtained. The open loop speed control was achieved by maintaining V/f ratio at constant value. The simulation results show that the proposed system effectively controls the motor speed and enhances the drive performance through reduction in total harmonic distortion (THD). This drive system can be used energy saving in variable torque load applications like boiler feed pumps conveyors, rolling mills, printing machines etc.

#### 8. REFERENCES

- [1] S. Malik and D. Kluge, "ACS 7000 world's first standard ac drive for Medium-voltage applications," *ABB Rev.*, no. 2, pp. 4–11, 2006.

- [2] H. Natchpong, Y. Kondo, and H. Akagi, "Five-level diode clamped PWM converters connected back-to-back for motor drives," *IEEE Trans.Ind. Appl.*, vol. 44, no. 4, pp. 1268–1276, Jul./Aug. 2008.

- [3] T. S.Key and J. S. Lai, "IEEE and international harmonic standards impact on power electronic equipment design," in *Conf. Rec. IEEE IECON*, Nov.2005, vol. 2, pp. 430–436.

- [4] F. DeWinter, N. Zargari, S. Rizzo, and X. Yuan, "Medium voltage drives: Are isolation transformers required?," in *Conf. Rec. IEEE IAS PetroleumChem. Ind. Conf.*, 2002, pp. 191–196.

- [5] B.Wu, *High-Power Converters and AC Drives*. Piscataway, NJ: IEEE Press, 2006.

- [6] Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter," *IEEE Trans. Ind. Appl.*, vol. IA-17, no. 5, pp. 518–523,Sep. 2008.

- [7] L. M. Tolbert, F. Z. Peng, and T. G. Habetler, "Multilevel converters for large electric drives," *IEEE Trans. Ind. Appl.*, vol. 35, no. 1, pp. 36–44, Jan. /Feb. 2003.

- [8] J.S.Lai and F. Z. Peng, "Multilevel converters—A new breed of power converters," *IEEE Trans. Ind. Appl.*, vol. 32, no. 3, pp. 509–517, May/Jun.2002.

- [9] J.Rodriguez, J.S.Lai, and F.Z.Peng, "Multilevel inverter: A survey of topologies, control, and applications," *IEEE Trans. Ind. Electron.*, vol. 49,no. 4, pp. 724–738, Aug. 2002.

- [10] C. Newton, M. Sumner, and T. Alexander, "Multi-level converters: A real solution to high voltage drives?" in *Inst. Electr. Eng. (IEE) Colloq. New Power Electron. Tech. Dig.*, no. 1997/091, pp. 3-1–3-5, 1999.

- [11] Newton and M. Sumner, "Novel technique for maintaining balanced internal DC link voltages in diode

- clamped five-level inverters," *Proc.Inst. Electr. Eng.* (*IEE*) *Power Appl.*, vol. 146, no. 3, pp. 341–349, 1999.

- [12] S. Ogasawara and H. Akagi, "Analysis of variation of neutral point potential in neutral-point-clamped voltage source PWM inverters," in *Conf.Rec. IEEE IAS Annu. Meeting*, 1993, vol. 2, pp. 965–970

- [13] M.Marchesoni and P.Tenca, "Diode clamped multilevel converters: A practicable way to balance DC-link voltages," *IEEE Trans. Ind. Electron*, vol. 49, no. 4, pp. 752–765, Aug. 2002.

- [14] Z. Pan, F. Z. Peng, K. A.Corzine, V.R.Stefannovic, J.M.Leuthen, and S. Gataric, "Voltage balancing control of diode clamped multilevel rectifier/inverter systems," *IEEE Trans. Ind. Appl.*, vol. 41, no. 6, pp. 1698–1706, Nov./Dec. 2005.

- [15] S. Ali Khajehoddin, Alireza Bakhshai, and Praveen K. Jain," A Simple Voltage Balancing Scheme for m-Level Diode-Clamped Multilevel Converters Based on a Generalized Current Flow Model," *IEEE trans.power electron.*, vol. 23, no. 5, September 2008.

- [16] J. Pou, R. Pindado, and D. Boroyevich, "Voltage-balance limits in four level diode clamped converter with passive front ends," *IEEE Trans Ind. Electron.*, vol. 52, no. 1, pp. 190–196, Feb. 2005.

- [17] H. Akagi, H. Fujita, S. Yonetani, and Y. Kondo, "A 6.6-kV transformer less STATCOM based on a five-level diode clamped PWM converter: System design and experimentation of a 200-V, 10-kVA laboratory model," *IEEETrans. Ind. Appl.*, vol. 44, no. 2, pp. 672–680, Mar. 2008

- [18] S. Busquets-Monge, S. Alepuz, J. Bordonau, and J. Peracaula, "Voltage balancing control of diode clamped multilevel converters with passive front-ends," *IEEE Trans. Power Electron.*, vol. 23, no. 4, pp. 1751–1758,Jul. 2008.

- [19] R. Rojas, T. Ohnishi, and T. Suzuki, "PWM control method for a four level inverter," *Proc. Inst. Electr. Eng. (IEE) Power Appl.*, vol. 142, no. 6,pp.390–396,1995.