# NEUTRAL POINT POTENTIAL BALANCING ALGORITHM FOR SLIDING MODE CONTROLLED THREE-LEVEL ACTIVE POWER FILTER

#### T. ABDELKRIM K. BENAMRANE

Applied Research Unit on Renewable Energies, Industrial zone, B.P. 88, Ghardaïa, Algeria. Tel: 0021329870126, Fax: 0021329870152, Email: tameur2@yahoo.fr

#### E.M. BERKOUK

Laboratory of Process Control, Polytechnic National School, Street Hassen Badi, El Harrach, B.P. 182 Algiers, Algeria.

## T. BENSLIMANE

University of Msila, BP. 166, street Ichbilia, 28000 Msila, Algeria. Email: bens082002@yahoo.fr

Abstract: In this paper, the authors present a study of the instability problem of the input DC voltages of the threelevel Neutral Point Clamping (NPC) Active Power Filter (APF). This APF is applied for the enhancement of voltage network power quality by compensation of harmonic currents produced by a nonlinear load. In the first part, the authors present a topology of three-level NPC Voltage Source Inverter (VSI), and its space vector diagram. In the second part, as solution for instability problem of the input DC voltages of the APF, the authors propose a simplified Space Vector Pulse Width Modulation (SVPWM) with neutral point potential control. After that, the sliding mode regulator used to control the APF is developed. Stable DC bus supply associated with sliding regulator of APF allows getting low harmonic content network currents with unity power factor.

**Key words:** Active power filter, NPC multilevel inverter, space vector pulse width modulation (SVPWM), Neutral point potential control, nonlinear load.

#### 1. Introduction

The widespread use of power electronics in domestic and industrial application had induced power line losses and electrical interference problems, which resulted in low power factor, efficiency and bad quality of the power electrical distribution system.

Classical solutions use passive filters, made up of capacitors and inductors, to reduce line current harmonics and to compensate reactive power. But these filters have several drawbacks: risk of parallel and series resonance with the AC source, bulky passive components, and low flexibility due to fixed compensation characteristics.

An alternative solution is to use active power filters, especially the shunt filter, which is the most suitable for harmonic current elimination and reactive power compensation [1].

The structures of the filters knew an evolution, from two-level converters [2,3] to multilevel

converters [4-6]. Various topologies are developed such as flying capacitor multilevel converters, diode clamped multilevel converters, NPC multilevel converters, and H bridge multilevel converters.

The unbalance of the different DC voltage sources of the three-level (NPC) active power filters constitutes the major limitation for the use of these power converters.

Several methods are proposed to suppress the unbalance of neutral point potential, generally using redundant vectors. Some of these methods are based on adding a zero sequence or a dc-offset to output voltage [7,8]. In [9,10], power electronics circuitry is added to redistribute charges between capacitors. A method based on minimizing a quadratic parameter that depends on capacitor voltages is presented in [11]. This quadratic parameter is positively defined and reach zero when the two capacitors have the same voltage. Some other works use a converter-inverter cascade [12], and apply automatic control methods, such as fuzzy logic control [13] or sliding mode control [14] to this cascade. The drawback of these methods is either high costs and system complexity, or the use of open loop scheme. In this work we use a simple and closed loop method which makes a continuous measurement of output current and difference between capacitors voltages, and choose the redundant vector on the basis of these measurements.

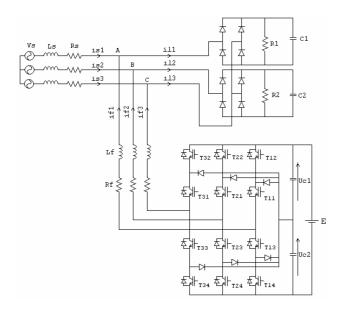

In this paper, first part is dedicated to the presentation of the model of the three phases three-level NPC VSI with its space vector diagram. In the second part, the simplified SVPWM algorithm with the proposed neutral point potential control algorithm are presented. This APF is applied for the enhancement of voltage network power quality by compensation of harmonic currents produced by a nonlinear load (Fig. 1). At the end the simulation results of sliding mode controlled APF are presented.

Fig. 1. Synoptic diagram of application of shunt APF on power supply fed nonlinear load

### 2. Modelling of three-level NPC voltage source inverter

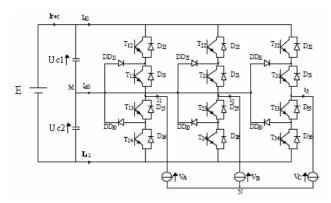

The three phases three-level NPC VSI is constituted by three legs and two DC voltage sources. Each leg has four bi-directional switches in series, and two diodes to get the zero voltage for  $V_{KM}$  (Fig. 2). Each switch is composed by a transistor and a diode in anti-parallel [15].

The switch connection function  $F_{KS}$  indicates the

opened or closed state of the switch

$$T_{KS}$$

:

$$F_{KS} = \begin{cases} 1 & \text{if } T_{KS} \text{ close} \\ 0 & \text{if } T_{KS} \text{ open} \end{cases}$$

(1)

For a leg K of the three phases three-level NPC VSI, several complementary control laws are possible. The optimal control law of this inverter is:

Fig. 2. Three-level NPC voltage source inverter

$$\begin{cases}

F_{K4} = 1 - F_{K1} \\

F_{K3} = 1 - F_{K2}

\end{cases}$$

(2)

Half leg connection function  $F_{Km}^{b}$  is defined as:

$$\begin{cases} F_{K1}^{\ b} = F_{K1} F_{K2} \\ F_{K0}^{\ b} = F_{K3} F_{K4} \end{cases}$$

m =1: for the lower half leg;

m = 0: for the upper half leg.

As indicated in Table 1, each leg of the inverter can have three possible switching states, P, O, or N. When the top two switches  $T_{i1}$  and  $T_{i2}$  are turned on, the switching state is P. When the medium switches T<sub>i2</sub> and T<sub>i3</sub> are turned on switching state is O. When the lower switches T<sub>i3</sub> and T<sub>i4</sub> are turned on, the switching state is N.

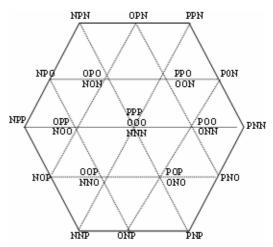

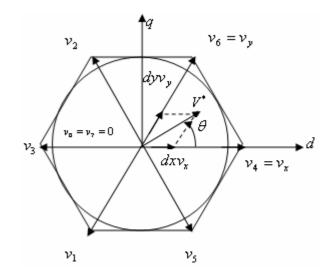

Fig. 3 shows the space vector diagram for threelevel inverter. Since three kinds of switching states exist in each leg, this converter has 27 switching states, as indicated in the diagram. The output voltage vector can take only 18 discrete positions in the diagram because some switches state are redundant and create the same space vector.

Fig. 3. Space vector diagram of a three-level inverter

# 3. Three-level inverter control

# a. Space vector modulation for two-level inverter

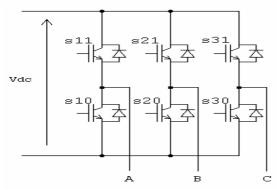

Fig. 4 shows structure of two-level inverter. Each one of the three phases of the inverter has two switches and two freewheeling diodes. Depending on the values of the switching signals, the two-level inverter has eight states, summarized in Table 2, where it is also indicated the output voltage vector produced in each state. These output vectors are shown on the space vector diagram of Fig. 5. It is also indicated an arbitrary reference vector  $V^*$ , to be generated by the

The desired voltage vector,  $V^*$ , located in a given sector, can be generated by a linear combination of the two adjacent base vectors, v<sub>x</sub> and v<sub>y</sub>, which are framing the sector, and one of the two zero vectors  $v_z$ .

$$V^* = d_x v_x + d_y v_y + d_z v_z$$

(4)

Table 1 States of three-level inverter

| Switching<br>Symbols | Sv       | Output<br>Voltage |                 |          |                  |

|----------------------|----------|-------------------|-----------------|----------|------------------|

|                      | $T_{i1}$ | $T_{i2}$          | T <sub>i3</sub> | $T_{i4}$ |                  |

| P                    | ON       | ON                | OFF             | OFF      | $U_{c1}$         |

| О                    | ON       | OFF               | ON              | OFF      | 0                |

| N                    | OFF      | OFF               | ON              | ON       | -U <sub>c2</sub> |

Fig. 4. Two-level inverter structure

Table 2 States of two-level inverter

| State | F <sub>a</sub> | $F_b$ | $F_c$ | Voltage<br>vector |

|-------|----------------|-------|-------|-------------------|

| 0     | 0              | 0     | 0     | $V_0$             |

| 1     | 0              | 0     | 1     | $V_1$             |

| 2     | 0              | 1     | 0     | $V_2$             |

| 3     | 0              | 1     | 1     | $V_3$             |

| 4     | 1              | 0     | 0     | $V_4$             |

| 5     | 1              | 0     | 1     | $V_5$             |

| 6     | 1              | 1     | 0     | $V_6$             |

| 7     | 1              | 1     | 1     | $V_7$             |

$d_x$ ,  $d_y$  and  $d_z$  denotes the so called duty ratios of states X, Y and Z of the inverter within the switching interval, respectively.

The duty ratios  $d_x$ ,  $d_y$  and  $d_z$  are calculated as [16,17]:

$$d_{x} = \frac{\left|V^{2*}\right|}{\sqrt{2/3}V_{dc}} \frac{\sin(60 - \theta)}{\sin(60)}$$

$$d_{y} = \frac{\left|V^{2*}\right|}{\sqrt{2/3}V_{dc}} \frac{\sin(\theta)}{\sin(60)}$$

$$d_{z} = 1 - d_{x} - d_{y}$$

(5)

# b. Simplified SVPWM for three-level inverter

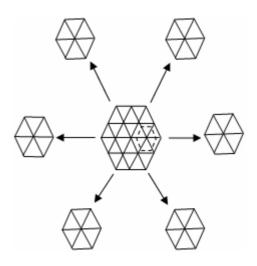

In this work, we present a simple and fast method that divides the space vector diagram of three-level inverter into six small hexagons. Each hexagon is space vector diagram of two-level inverter, as shown in Fig. 6.

Fig. 5. Space vector diagram of two-level inverter

Fig. 6. Decomposition of space vector diagram of a three-level inverter to six hexagons

Fig. 7. Division of overlapped regions

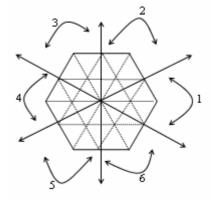

To reach this simplification, two steps have to be done. Firstly, from the location of the given reference voltage, one hexagon has to be selected among the six small hexagon of the three-level space vector diagram.

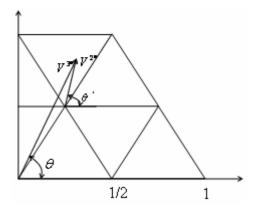

There exist some regions that are overlapped by two adjacent small hexagons. These regions will be divided in equality between the two hexagons as shown in Fig. 7. Each hexagon is identified by a number S defined in equation (6). Secondly, we translate the origin of the reference voltage vector towards the center of the selected hexagon as indicated in Fig. 8. This translation is done by subtracting the center vector of selected hexagon from the original reference vector. Table 3 gives the components d and q of the reference voltage  $V^{2*}$  after translation, for all the six hexagons. The index  $(^2)$  or  $(^3)$  above the components indicate two or three-level cases respectively.

$$s = \begin{cases} 1 & \text{if } -\pi/6 < \theta < \pi/6 \\ 2 & \text{if } \pi/6 < \theta < \pi/2 \\ 3 & \text{if } \pi/2 < \theta < 5\pi/6 \\ 4 & \text{if } 5\pi/6 < \theta < 7\pi/6 \\ 5 & \text{if } 7\pi/6 < \theta < 3\pi/2 \\ 6 & \text{if } 3\pi/2 < \theta < 11\pi/6 \end{cases}$$

(6)

Fig. 8. Translation of reference voltage vector

Table 3

Correction of reference voltage vector

| Correction of reference voltage vector |                  |                         |  |  |

|----------------------------------------|------------------|-------------------------|--|--|

| S                                      | $v_d^{2*}$       | $v_q^{2*}$              |  |  |

| 1                                      | $v_d^{3*} - 1/2$ | $v_q^{3*}$              |  |  |

| 2                                      | $v_d^{3*} - 1/4$ | $v_q^{3*} - \sqrt{3}/4$ |  |  |

| 3                                      | $v_d^{3*} + 1/4$ | $v_q^{3*} - \sqrt{3}/4$ |  |  |

| 4                                      | $v_d^{3*} - 1/2$ | $v_q^{3*}$              |  |  |

| 5                                      | $v_d^{3*} + 1/4$ | $v_q^{3*} + \sqrt{3}/4$ |  |  |

| 6                                      | $v_d^{3*} - 1/4$ | $v_q^{3*} + \sqrt{3}/4$ |  |  |

### C. Neutral Point potential control method

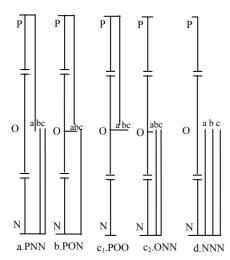

In the space vector diagram of three-level inverter (Fig. 3), we can distinguish four types of vectors: large vectors, medium vectors, small vectors and zero

vectors. The large vectors are the vectors that all of three legs are connected to either point P or N, except in the case of all the three being connected at the same point. There are six large vectors in the space vector diagram: PNN, PPN, NPN, NPP, NNP and PNP. The medium vectors are the ones that only one phase is connected to point O and other two phases are connected to P and N each other. There are six medium vectors: PON, OPN, NPO, NOP, ONP and PNO. The small vectors are those vectors that have two phases connected at the same point. There are twelve of them: PPO, OON, OPO, NON, OPP, NOO, OOP, NNO, POP, ONO, POO and ONN. The zero vectors are the vectors that have all three phases are connected at the same point. There are three zero vectors: PPP, OOO and NNN.

To show the effect of each type of vectors on the neutral point potential, we present the load connections of one example of each type in Fig. 9. It may be easily deduced from Fig. 9.a and Fig. 9.d that neither zero vectors nor large vectors inject current in the neutral point O. So they do not change the voltage of neutral point.

Fig. 9.b shows that medium vectors can inject current in the neutral point. Fig. 9.c1 and Fig. 9.c2 show two small vectors with two different switching combinations: POO and ONN. These two vectors product the same output voltage, but when the vector POO is applied, the current flows into the neutral point  $(I_{d0} = -i_1)$ , while with the vector ONN, the current flows out  $(I_{d0} = i_1)$ (Fig. 2).

Table 4 shows the current injected by all small and medium vectors [18]. As we see, each small redundant vector can inject either positive or negative current. Those small vectors injecting positive phase currents into the neutral point will be called positive vectors (ONN, PPO, NON, OPP, NNO, POP), while those injecting opposite phase currents will be called negatives vectors (POO, OON, OPO, NOO, OOP, ONO).

Medium vectors also affect neutral point potential. However, as they are not redundant vectors, this influence will not be controlled, being therefore considered as perturbation for the dc-voltage stabilization [19,9]

The neutral point potential control is based on the use of both two redundant vectors in each sector, in order to inject positive or negative current in neutral point, depending on the value of the two capacitors voltages and the load current (7).

$$c\frac{dU_{c1}}{dt} = I_{red} - I_{d1}$$

$$c\frac{dU_{c2}}{dt} = I_{red} + I_{d2}$$

$$I_{d0} = -(I_{d1} + I_{d2})$$

$$I_{d1} = F11 \cdot F12 \cdot i_1 + F21 \cdot F22 \cdot i_2 + F31 \cdot F32 \cdot i_3$$

$$I_{d2} = F13 \cdot F14 \cdot i_1 + F23 \cdot F24 \cdot i_2 + F33 \cdot F34 \cdot i_3$$

(7)

Fig. 9. Neutral point connections

Table 5 shows the current injected by the six small vectors. By using this table, one proposes the neutral point potential control algorithm of this converter as indicated by (8) (9) (10).

Table 4

Neutral point current of different space vectors

| Positive<br>Small<br>vectors | $I_{d0}$ | Negative<br>Small<br>vectors | $I_{d0}$                | Medium<br>Vectors | $I_{d0}$ |

|------------------------------|----------|------------------------------|-------------------------|-------------------|----------|

| ONN                          | $i_1$    | POO                          | - <i>i</i> <sub>1</sub> | PON               | $i_2$    |

| PPO                          | $i_3$    | OON                          | - <b>i</b> <sub>3</sub> | OPN               | $i_1$    |

| NON                          | $i_2$    | OPO                          | - <i>i</i> <sub>2</sub> | NPO               | $i_3$    |

| OPP                          | $i_1$    | NOO                          | - i <sub>1</sub>        | NOP               | $i_2$    |

| NNO                          | $i_3$    | OOP                          | - <b>i</b> <sub>3</sub> | ONP               | $i_1$    |

| POP                          | $i_2$    | ONO                          | - <i>i</i> <sub>2</sub> | PNO               | $i_3$    |

Table 5

Neutral point current of small space vectors

| Vectors  | Redundancy (a) | $I_{d0}$ | Redundancy (b) | $I_{d0}$                |

|----------|----------------|----------|----------------|-------------------------|

| Vector 1 | ONN            | $i_1$    | POO            | - i <sub>1</sub>        |

| Vector 2 | PPO            | $i_3$    | OON            | - <i>i</i> <sub>3</sub> |

| Vector 3 | NON            | $i_2$    | OPO            | - <i>i</i> <sub>2</sub> |

| Vector 4 | OPP            | $i_1$    | NOO            | - <b>i</b> <sub>1</sub> |

| Vector 5 | NNO            | $i_3$    | OOP            | - <b>i</b> <sub>3</sub> |

| Vector 6 | POP            | $i_2$    | ONO            | - i <sub>2</sub>        |

### For vector 1 and vector 4

$$\begin{cases} if & U_{c1} \geq U_{c2} & \& & i_1 \geq 0 \implies \text{redundancy} & \text{(b)} \\ if & U_{c1} \geq U_{c2} & \& & i_1 \leq 0 \implies \text{redundancy} & \text{(a)} \\ if & U_{c1} \leq U_{c2} & \& & i_1 \geq 0 \implies \text{redundancy} & \text{(a)} \\ if & U_{c1} \leq U_{c2} & \& & i_1 \leq 0 \implies \text{redundancy} & \text{(b)} \end{cases}$$

For vector 2 and vector 5

$$\begin{cases} if & U_{c1} \ge U_{c2} & \& & i_3 \ge 0 \implies \text{redundancy (b)} \\ if & U_{c1} \ge U_{c2} & \& & i_3 \le 0 \implies \text{redundancy (a)} \\ if & U_{c1} \le U_{c2} & \& & i_3 \ge 0 \implies \text{redundancy (a)} \\ if & U_{c1} \le U_{c2} & \& & i_3 \le 0 \implies \text{redundancy (b)} \end{cases}$$

For vector 3 and vector 6

$$\begin{cases} if \quad U_{c1} \geq U_{c2} & \& \quad i_2 \geq 0 \implies \text{redundancy (b)} \\ if \quad U_{c1} \geq U_{c2} & \& \quad i_2 \leq 0 \implies \text{redundancy (a)} \\ if \quad U_{c1} \leq U_{c2} & \& \quad i_2 \geq 0 \implies \text{redundancy (a)} \\ if \quad U_{c1} \leq U_{c2} & \& \quad i_2 \leq 0 \implies \text{redundancy (b)} \end{cases}$$

#### 4. Active Power Filter Control

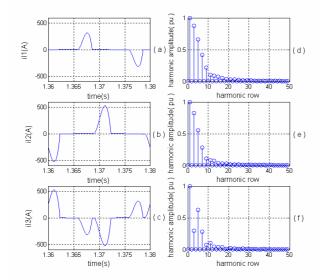

A voltage source of 220V, 50Hz feeds a three phases nonlinear load illustrated in Fig. 1. This load produces distorted phases currents with THD of respectively 120%, 104 % and 76% which is above the tolerated THD limit standard. These currents with their spectral analysis are presented in Fig. 10.

Active power filter is controlled using sliding mode regulator [20,21]. From the model of active filter associated to supply network (11) and by considering the error between harmonic current reference and the active filter current as sliding surface (12), and the smooth continuous function as attractive control function (13), one gets the control law (14).

$$V_{frefK} - V_K = R_f i_{fK} + L_f \frac{di_{fK}}{dt}$$

$$di_{frefK} = R_f i_{fK} + L_f \frac{di_{fK}}{dt}$$

(11)

with:

$$V_K = V_{SK} - R_s i_{SK} - L_s \frac{di_{SK}}{dt}$$

;

$$K = 1.2 \text{ and } 3$$

$$S_s = i_{frefK} - i_{fK} \tag{12}$$

$$U_n = k \cdot \frac{S_s}{|S_s| + \lambda} \tag{13}$$

$$V_{frefK} = R_f i_{fK} + L_f \frac{di_{frefK}}{dt} + V_K + k \frac{S_s}{|S_s| + \lambda}$$

(14)

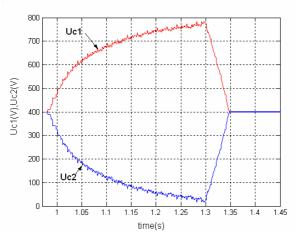

Fig. 11 shows the DC bus capacitors voltages of three-level APF. We can note that the capacitors voltages difference increases continuously. The application of SVPWM with neutral point potential control at t=1,3s pushes these voltages toward the reference of E/2 keeping them equal.

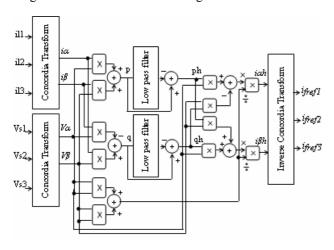

Instantaneous real and imaginary powers method is used to identify reference harmonic currents. Its algorithm is presented in Fig. 12.

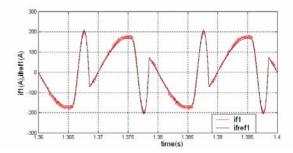

Reference identified harmonic current  $i_{frefl}$  and output filter current  $i_{fl}$  are almost superimposed as presented in Fig. 13.

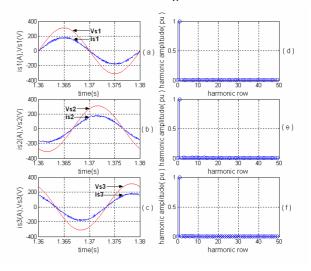

Fig. 14.a,b,c presents main source voltages and currents after harmonic currents compensation. Spectral analysis of each current is illustrated in Fig. 14.d,e,f. It is shown that source currents are

almost sinusoidal with THD of respectively 1.9%, 2.4% and 2.3% and unity power factor.

Fig. 10. Load currents

Fig. 11. DC bus condensers voltages of three-level APF

Fig. 12. Instantaneous real and imaginary powers harmonic current identification algorithm

Fig. 13. Reference harmonic current  $i_{frefl}$  and filter output current  $i_{fl}$

Fig. 14. Main source voltages and currents with their spectral analysis

### 5. Conclusion

In this paper, one studies the problem of unbalanced input capacitors DC voltages of three-level NPC shunt active power filter.

The study of the instability problem of the input DC voltages of this converter shows that its different input voltages are not stable, which implies a bad harmonic current compensation.

To solve this instability problem, one proposes to use a simple and closed loop method which makes a continuous measurement of output current and difference between capacitors voltages, and choose the redundant vector on the basis of these measurements.

The application of the proposed simplified SVPWM with neutral point potential control makes the input DC link voltages stable.

Stable DC bus supply of sliding mode controlled three-level NPC shunt APF allows getting balanced main source currents with low total harmonic distortion and unity power factor.

The results obtained in this work show that the proposed solution allows using this topology to compensate the harmonic current and reactive power in high power utilities.

### 6. Appendix

Main source:

$V_{ph-ph}$ = 380V,f=50Hz,  $R_s$  = 0.0001 $\Omega$ ,  $L_s$  = 0.0001H. Active power filter:

$E = 800V, R_f = 0.001\Omega, L_f = 0.0005H, C = 0.005F, f_c = 5kHz.$  Nonlinear load

R1=20 $\Omega$ , R2=10  $\Omega$ , C1=0.05F, C2=0.05F.

### References

- 1 Choe, G., Park, M.: *A new injection method for ac harmonic elimination by active power filter*. In: IEEE Transactions on Industry Applications, Vol. 35, No. 1, feb. 1988, p. 141-147.

- Ozdemir, E., Kale, M., Ozdemir, S.: A novel control method for active power filter under non-ideal mains voltage. In: Proc IEEE Conference on Control Applications CCA 2003, Vol. 2, 2003, p. 931-936.

- 3 Mendalek, N., Ai-Haddad, K.: Modeling and nonlinear control of shunt active power filter in the synchronous reference frame. In: Proc. Harmonics and Quality of Power, Vol. 1, 2000, p. 30-35.

- 4 Gupta, R., Ghosh, A., Joshi, A.: *Control of 3-level shunt active power filter using harmonic selective controller*. In: IEEE Power India Conference, 10-12 April, New Delhi, India, 2006.

- 5 Aburto, V., Schneider, M., Moran, L., Dixon, F.: *An active power filter implemented with a three-level NPC voltage-source inverter*. In: IEEE PESC'97 Record, Vol. 2, 1997, p. 1121-1126.

- 6 Lin, B.R., Chiang, H.K., Huang, C.H.: Three-phase three-level active power filter with a clamped capacitor topology. In: IEE Proc.-Electr. Power Appl., Vol. 153, No 4, 2006, p. 513-522.

- 7 Lee, Y.H., Kim, R.Y., Hyun, D.S.: A novel SVPWM strategy considering DC-link balancing for multi-level voltage source inverter. In: Fourteenth Annual IEEE on Applied Power Electronics Conference and Exposition, APEC'99, Vol. 1, 1999, p. 509-514.

- Newton, C., Summer, M.: Neutral point control for multi-level inverters: theory, design and operational limitations. In: IEEE Industry applications Society Annual Meeting, New Orleans, Louisiana, 1997, p. 1336-1343.

- 9 Lee, D.H., Lee, S.R., Lee, F.C.: An analysis of midpoint balance for the neutral-point -clamped three-levelVSI. In: 29th Annual IEEE Power Electronics Specialist Conference, PESC 98 record, Vol. 1, 1998, p. 193-199.

- Jouanne, A.V., Dai, S., Zhang, H.: A multilevel inverter approach providing DC-link balancing, through enhancement, and common-mode voltage elimination. In IEEE Transactions on industrial Electronics, Vol. 49, No. 4, 2002, p. 739-745.

- 11 Pou, J., Pindado, R., Boroyevich, D., Rodriguez, P., Vicente, J.: *Voltage balancing strategies for diode-clamped multilevel converters*. In: 35th Annual IEEE Power Electronics Specialists Conference, Aachen, Germany, 2004, p. 3988-3993.

- 12 Talha, A., Berkouk, E.M., Boucherit, M.S.: Study and control of two-level PWM rectifier-clamping bridge-seven-level NPC VSI cascade: application to PMSM speed control. In: European Transaction on Electrical Power, Vol. 16, Issue 1, 2005, p. 93-107.

- 13 Barkati, S., Berkouk, E.M., Boucherit, M.S.: Control of the DC-Buses of a seven-level diode-clamped inverter using type-2 fuzzy systems. In: The Mediterranean Journal of Measurement and Control, Vol. 2, No. 4, 2006, p. 161-168.

- 14 Chibani, R., Manesse, G., Berkouk, E.M.: A new solution to the unbalance problem of the input DC voltages of a five level NPC-VSI by using sliding mode regulation. In: 10th International Power Electronics and Motion Control, EPE-PEMC2002, Cavtat and Dubrovnik, Croatia, 2002.

- 15 Celanovic, N., Boroyevich, D.: A Comprehensive Study of Neutral-Point Voltage Balancing Problem in Three-Level Neutral-Point-Clamped Voltage Source PWM Inverters. In IEEE Transactions on Power Electronics, Vol. 15, No. 2, 2000, p. 242-250.

- Van Der Broeck, H.W., Skudelny, H.C., Stanke, G.V.: Analysis and Realization of a pulse width modulation based on voltage space vectors. In: IEEE Transactions on Industrial Applications, Vol. 24, No. 1, 1988, p. 142-150.

- 17 Lalili, D., Berkouk, E.M., Boudjema, F., Lourci, N.: Simplified space vector PWM algorithm for three-level inverter with neutral point potential control. In: The Mediterranean Journal of Measurement and Control, Vol. 3, No. 1, 2007, p. 30-39.

- 18 Celanvovic, N.: Space vector modulation and control of multilevel converters. Ph.D.thesis, Virginia Polytechnic Institute and State University, Blacksburg, Virginia, USA,2000.

- 19 Liu, Y., Wu, X., Huang, L.: Implementation of three-level inverter using a novel Space vector modulation algorithm. In: Proc. IEEE Conf. on Power System Technology, PowerCon 2002, Vol. 1, p. 606-610.

- 20 Slotine, J.J., Li, W.: *Applied Nonlinear Control*. Englewood Cliffs, NJ: Prentice-Hall, UK, 1991.

- 21 Utkin, V.I.: *Sliding mode control design principles and application to electric drives*. In: IEEE Trans On Elect, Vol 40, 1993, p. 23-36.