# Digital Simulation of ZVS DC to DC Converter using Simulink

R. Madhusudhanan Research scholar Sathyabama university Chennai, India S.Rama Reddy Professor Jerusalem college of engineering Chennai, India

#### Abstract:

This paper presents digital simulation of ZVS half bridge DC to DC converter with modified PWM control. The switching losses are reduced by using soft switching. Conventional and duty cycle shifted PWM DC to DC converters are simulated using matlab simulink and the results are presented. The principle of operation and the key features of modified PWM DC to DC converter are also presented.

#### I. Introduction

Several new techniques for high frequency DC-DC conversion have been proposed to reduce component stresses and switching losses while achieving high power density and improved performance [1]-[11]. Among them, the phase-shifted zero-voltage-switching (ZVS) full bridge [1]-[3] is one of the most attractive techniques since it allows all switches to operate at ZVS by utilizing transformer leakage inductance and metal oxide semiconductor field effect transistors (MOSFETs) junction capacitance without adding an auxiliary switch. However, the complexity of the full-bridge is almost highest among the conventional topologies due to its large switch count and complicated control and driving. Active-clamp forward topology [4]-[6] is another typical example to successfully realize ZVS for the switches by utilizing the leakage inductance, magnetizing inductance and junction capacitance. However, the topology of the converter is asymmetric and the energy-delivery is unidirectional. In other words, voltage and current stresses being higher compared to symmetric half-bridge and full-bridge converters. This disadvantage limits power level of the active-clamp forward topology applications. In addition, dc bias of magnetizing current may exits in the transformer [5].

Half bridge (HB) DC-DC converter is an attractive topology for middle power level applications owing to its simplicity. There are two conventional control schemes for the HB DC-DC converter, namely, symmetric control and asymmetric (complimentary) control. The main drawback of the conventional symmetric control is that both primary switches in the converter operate at hard switching condition. Moreover, during the off-time period of two switches, the oscillation between the transformer leakage inductance and junction capacitance of the switches results in energy dissipation and electromagnetic interface (EMI) emissions due to reverse recovery of MOSFETs body diodes. To suppress the ringing, resistive snubbers are usually added. As a result, energy in the transformer leakage inductance is significantly dissipated in snubbers. Therefore, the symmetric-control half bridge is not a good candidate for high switching frequency power conversion.

The asymmetric (complimentary) control was proposed to achieve ZVS operation for HB switches [7]-[11]. Two drive signals are complementarily generated and applied to high side and low side switches may be turned on at ZVS conditions owing to the fact that the transformer primary current charges and discharges the junction capacitance. However, asymmetric stresses distribution on the corresponding components may occur due to the asymmetric duty cycle distribution for the two primary switches are not identical and voltage and current stresses on secondary rectifiers with higher voltage rating are needed at the penalty of degrading the performance and efficiency of the rectifier stage [10]. Furthermore, the DC gain ratio of the converter is nonlinear, thus higher duty cycle variation is needed for the same input voltage variation in comparison with symmetric PWM control scheme, which makes the converter operate further beyond the optimum operation point at high input voltage [10]. Therefore, the complementary (asymmetric) PWM control is more suitable for applications where the input voltage is fixed. As a solution to reduce the duty cycle variation for wide

input voltage range, an asymmetric transformer turns ratio together with integrated-magnetic structure was proposed in [10], such that rectifiers with lower withstanding voltage may be used to improve the performance. However, the power delivery of the current stresses in the switches and rectifiers are still uneven [10].

In this paper, a new control scheme, to be known as duty-cycle shifted PWM (DCS PWM) control, is proposed and applied to the conventional HB DC-DC converter to achieve ZVS for one of the two switches without adding extra components and without adding asymmetric penalties of the complementary control. The concept of this new control scheme is shifted one of the two symmetric PWM driving signals close to the other, such that ZVS may be achieved for the lagging switch due to the shortened resonant interval. Unlike the asymmetric control, the width of the duty cycle for the two switches is kept equal, such that all corresponding components work at the conditions with even stresses as the case in the symmetric control scheme.

Moreover, based on the DCS PWM control, a new half-bridge topology is proposed to achieve ZVS for the other switch and auxiliary switch by adding an auxiliary switch and diode in the conventional half bridge. ZVS for the other switch is achieved by utilizing the energy trapped in the leakage inductance. In additional, the proposed topology with DCS PWM control eliminates the ringing result from the oscillation between the transformer leakage inductance and the switches junction capacitances during the off-time period. Therefore, the proposed converter has a potential to operate at higher efficiencies and switching frequencies. The principle of operation and features of the DCS PWM control and proposed topologies are illustrated and verified experimentally on 36-75 V input voltage prototypes.

Section II describes the DCS PWM control scheme. Section III presents the principle of operation and feature of the proposed ZVS half-bridge topology with the DCS PWM control scheme. In the section IV, a modified DCS controlled ZVS HB topology is presented. Simulation results and conclusion are presented in sections iv and v respectively.

### **II. DCS PWM Control Scheme**

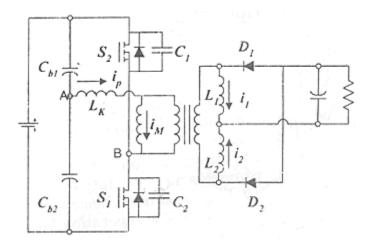

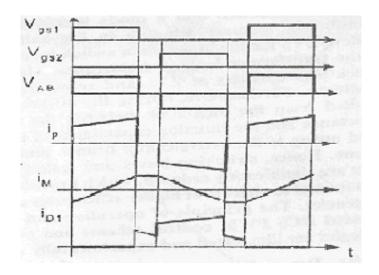

Fig.1 shows the half-bridge dc-dc converter with current double rectifier. The ideal waveforms for the symmetric PWM control is sketched in Fig 2(a), where  $L_{k_i}$  is the leakage inductance; ip,i<sub>m\_i</sub> are the transformer primary-side input and magnetizing currents, respectively; and i<sub>D1</sub> is the forward current through rectifier diode D1. Besides the hard switching, conventional symmetric PWM control has transformer-leakage-inductance related disadvantages. During the off-time period when both switches are off, the energy stored in the transformer leakage inductance may be recycled to primary dc bus through body diodes of MOSFETs. However, because of reverse recovery current of body diodes, the oscillation between the transformer leakage inductance and the MOSFETs junction capacitance is significant on the primary side. To suppress the ringing, usually, snubber circuits are necessarily added, but losses dissipated in the snubber become dramatically large, especially at high input current and high switching frequencies.

Fig.1 Conventional half bridge converter with a current double rectifier.

Fig.2a Symmetric PWM control.

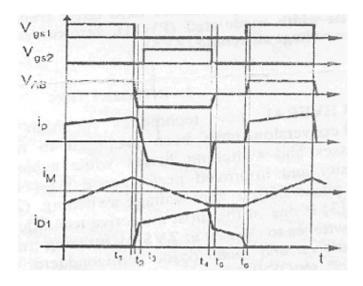

Fig.2b DCS PWM control.

## A. Proposed DCS PWM Control Scheme

Fig 2(b) shows the key waveforms of the half-bridge converter with the proposed DCS PWM control. Based on symmetric PWM control, S2 driving signal Vgs2 is shifted left such that the Vgs2 rising edge is close to the falling edge of S1 driving signal Vgs1. When S1 is turned off, the transformer primary current charges the junction capacitance of switch S2. After the voltage across drain-to-source of S2 drops to zero, the body diode of S2 conducts to carry the current. During the body diode conduction period, S2 may be turned on at zero-voltage switching. No ringing occurs during the transition period.

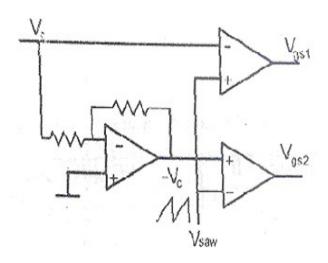

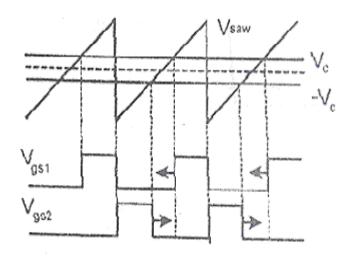

Fig.3a Modulation circuit.

Fig.3b Key waveforms

## Fig3.DCS PWM modulation scheme

Fig.3 shows a possible modulation approach for the realization of DCS PMW control. Where, saw is the SAW carrier waveform for modulation; Vc and -Vc are control voltages derived from the front voltage or current controller. By modulating Vc and -Vc, driving signals for S1 and S2 can be generated, respectively. Because the falling time of the saw waveform is short, the falling edge of S1 is always close to the rising edge of S2, which provide a possibility of ZVS for S2. This modulation method differs from the conventional symmetric PMW method in that the direction of variation of the two duty cycle is opposite as shown in Fig.3b. by the arrows shown on the driving signals waveforms. In other words, since Vc and -Vc are symmetrically centered around zero, the duty cycle of S1 is regulated by moving its rising edge left and right, while the duty cycle of S2 is regulated by moving its falling edge right and left, keeping S1 and S2 with the same duty cycle.

#### **III.Principle of Operation**

To simplify the analysis of operation, components are considered idle except otherwise indicated. The main operation modes are described as follows.

**Mode 1** ( $t < t_1$ ): Initially,  $S_1$  is conducting, and the input power is delivered to the output.  $L_1$  is charged and  $L_2$  freewheels through  $D_2$ .

**Mode 2** ( $t_1 < t < t_2$ ):  $S_1$  is turned off at  $t = t_1$ , causing the primary current lp to charge  $C_1$  and discharge  $C_2$ . During the interval, the reflected secondary inductor current dominates the primary current lp. Thus,  $C_2$  may be discharged to zero at wide load range, which means wide ZVS range can be achieved for  $S_2$ .

**Mode 3** ( $t_2 < t < t_3$ ): When the voltage across  $C_2$  is discharged to zero at  $t = t_2$ , the body diode of  $S_2$  conducts to carry the current, which provides ZVS conditions for switch  $S_2$ . During this period, leakage inductance is reset and secondary current  $I_1$  and  $I_2$  freewheel through  $D_1$  and  $D_2$ , respectively.

**Mode 4** ( $t_3 < t_4$ ):  $S_2$  is turned on with ZVS at  $t = t_3$ ; the primary current decreases to zero and then becomes negative. When the negative peak current equals to the reflected  $L_2$  current, the diode  $D_2$  is blocked and converter starts to deliver power to the output. The inductor  $L_2$  is charged and inductor  $L_1$  current continues to freewheel.

**Mode 5** ( $t_4 < t < t_5$ ):  $S_2$  is turned off at  $t = t_4$ , causing the primary current Ip to charge  $C_2$  and discharge  $C_1$ . When the secondary current  $D_1$  and  $D_2$  start to freewheel, leakage inductance and junction capacitance of switches  $S_1$  and  $S_2$  start to oscillate on the primary side. During the interval, body diodes may be involved, which worsens the ringing and results in recovery losses. (The ringing waveforms forms are not shown in figure.)

**Mode 6** ( $t_5 < t_6$ ): The oscillation comes to the end with equal voltage across switches S1 and S2. On the secondary side,  $L_1$  and  $L_2$  keep freewheeling. At  $t = t_6$ ,  $S_1$  is turned on again going back to Mode 1.

### Main Features Compared With Symmetric And Asymmetric PWM Controller

Compared with the conventional symmetric PWM controller, DCS PWM controlled HB has the same voltage and current stresses in the primary switches, and although the transformer voltage and current waveforms are different from those of the symmetric PWM control, the voltage-second value and magnetizing B-H of the transformer are identical. The peak and *rms* currents through the transformers are also the same for both schemes. Hence, there is no change in characteristics and design of the transformer from the symmetric PWM control to DCS PWM control.

In the secondary side, as shown in Fig.2, even though the currents through rectifiers have different waveforms in the two schemes, the peak and *rms* values of the waveforms are equal. Moreover the inductors voltage-second value, current peak and current rms values are the same for both schemes. Therefore, the voltage and current stresses for the secondary-side switches and inductors are the same for both schemes. Consequently, there is no change of control scheme from symmetric PWM control to the proposed DCS PWM control.

As mentioned above, both symmetric PWM and DCS PWM have even voltage and current stresses in corresponding components thanks to the identical duty cycle width for two switches. Hence, there are asymmetric penalties in asymmetric PWM control, which allows DCS PWM control to be employed in application for wide input voltage range. Furthermore, in the DCS PWM control, ZVS for switch S2 is achieved with out adding additional components. In addition, wide ZVS range operation may be achieved because the secondary inductor current is reflected to transformer primary side to the discharge the output capacitor of switch S2 to create ZVS condition for switch S2 to create ZVS condition for switch S2. Because switching losses and transformer leakage-inductance-related losses are reduced, higher efficiency is expected with the DCS PWM control method.

A comparison between the asymmetric HB, symmetric HB and DCS HB under same design conditions is shown in table 1, where N is the transformer turn ratio, D is the duty cycle of the switch S1, lo is the load current, Vin is the input voltage, and Vout is the output voltage. The filter inductance and output capacitance values are assumed large enough such that the inductor currents and output voltage is regarded as constant current source and constant voltage source, respectively. From Table 1, it can be observed that DCS HB has the same stresses distribution as the symmetric HB, while asymmetric HB has asymmetric stress distribution, dc bias of magnetizing current and nonlinear DC gain. This feature makes asymmetric HB unsuitable for applications with wide input voltage range.

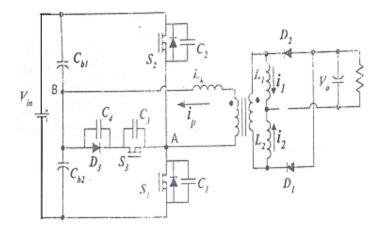

Fig.4 Proposed DCS controlled ZVS HB DC-DC converter

Fig.5 Key waveforms for the DCS controlled DC-DC converter.

In DCS controlled HB converter, the current waveforms and values through inductors L1 and L2 are same as those of the symmetric HB converter. In the symmetric HB converter, the inductor current ripples are interleaved, thus the output current ripple cancellation is achieved at the whole duty range (0 < D < 0.5). In other words, output current ripple is always smaller than individual inductor current ripple. However, in the DCS HB converter, the current cancellation is weekend due to the shifted duty cycle. Analysis shows the current cancellation takes effect only at the duty cycle range of 0.33 < D < 0.5, which means the current cancellation is lost at the duty cycle range of 0 < D < 0.33.

#### IV. Simulation Results

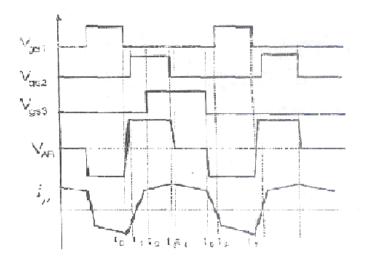

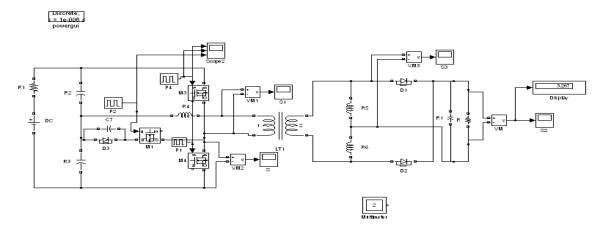

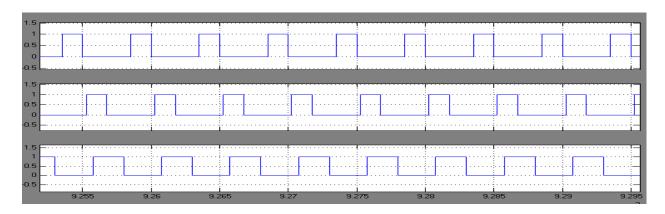

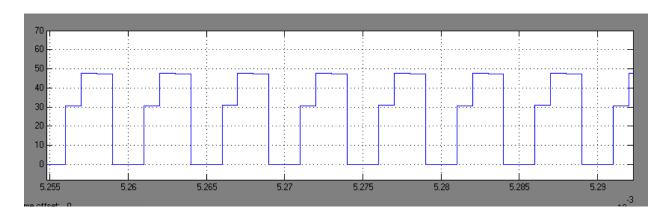

The simulation is done using matlab simulink and the results are presented here. The circuit of ZVS HB DC to DC connecter is shown in Fig.6a.Driving pulses for the MOSFETs are shown in Fig.6b.The voltage across M4 is shown in Fig.6c.Voltage across the primary of the transformer is shown in Fig. 6d.Voltage across the secondary of the transformer is shown in Fig. 6f.DC output voltage is shown in Fig.6g.

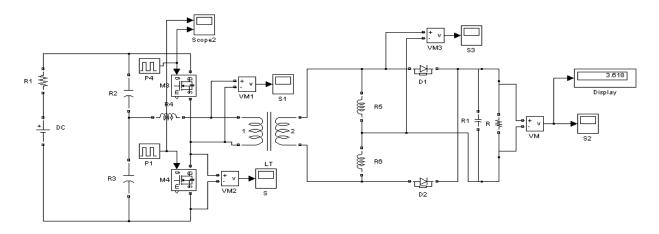

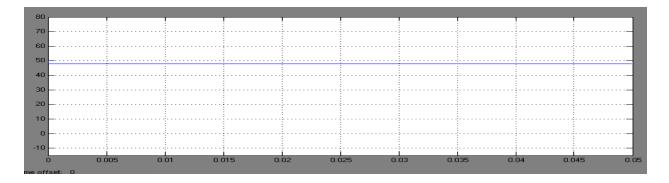

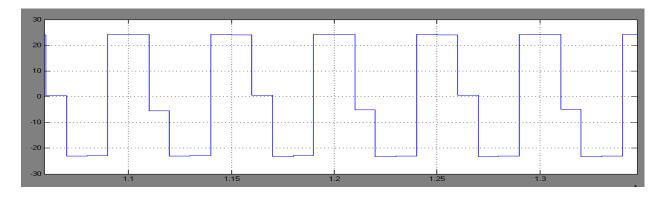

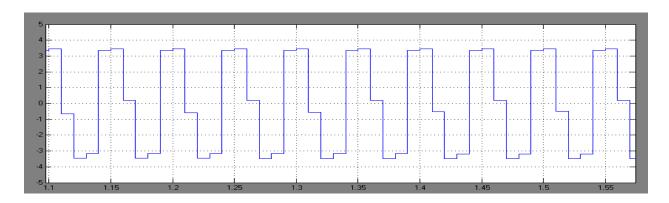

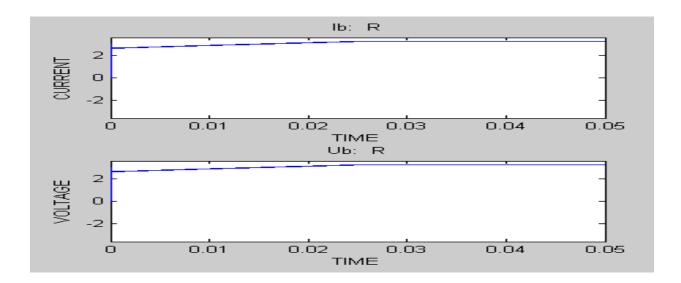

Modified ZVS PWM DC to DC converter is shown in Fig.7a.Input voltage is shown in Fig.7b.Triggering pulses are shown in Fig.7c.Voltage across switch S2 is shown in Fig.7d.The voltage across the primary is shown in Fig.7e.The voltage across secondary is shown in Fig.7f.Output voltage and current are shown in Fig.7g.

Fig.6a.Circuit diagram of ZVS Half Bridge DC – DC Converter

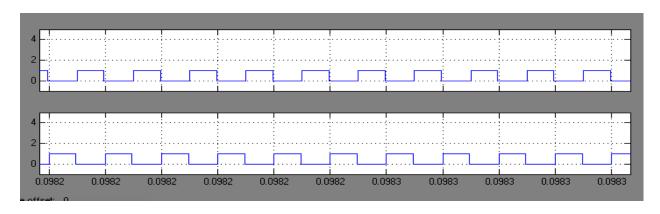

Fig.6b. Triggering pulses

Fig.6c.Voltage across switch M4

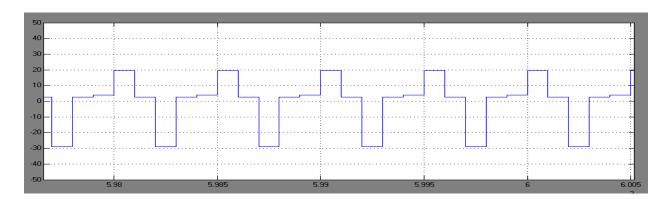

Fig.6d.Transformer primary voltage

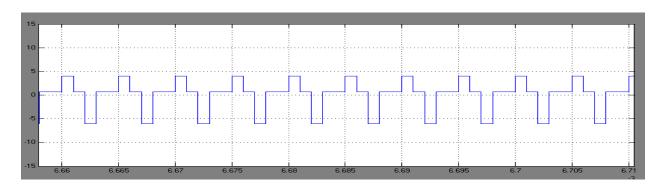

Fig. 6e. Transformer secondary side voltage

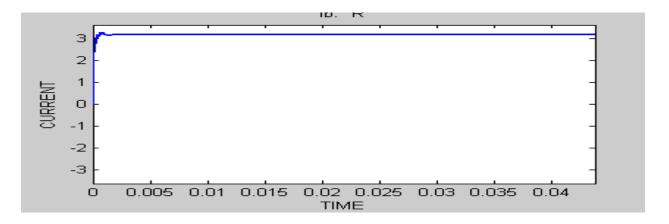

Fig.6f.Output current

Fig.6g. Output voltage

Fig.7a.Circuit diagram

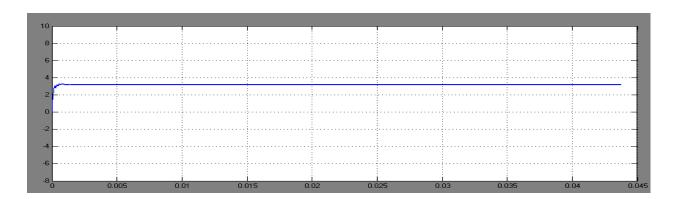

Fig.7b. Input voltage

Fig.7c.Trigerring pulses

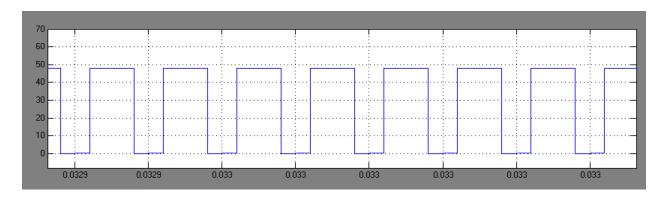

Fig.7d. Voltage across switch S2

Fig.7e.Transformer primary side voltage

Fig.7f.Transformer secondary side voltage

Fig.7g.Output voltage and current

### **V.Conclusion**

A simple duty cycle shifted PWM DC to DC converter is analysed and simulated. Power density is increased since it operates at high switching frequency. Pulse widths of the switches are calculated and the same are used for simulation studies. Simulation results of conventional and modified ZVS PWM DC to DC converter are presented. The simulation results coincide with the predictions.

#### .REFERENCES:

- W.Chen, F.C Lee, M.M.Jovanovic, J.A.Sabate,"A comparative study of class of full bridge zerovoltage-switched PWM converters,"in Proc.IEEE Applied Power electronics Conf., 1995, pp.893-899.

- 2. R.Redl, N.O.Sokal and L.Balogh, "A novel soft switching full bridge converter analysis design considerations and experimental results at 1.5kw 100khz,"in IEEE Power Electronics Specialists Conf.Records 1990,pp.162-172

- 3. J. A.Sabate, V.Vlatkovuc, R.B.Ridley, F.C.Lee and B.L.Cho "design consideration for high voltage high power full bridge zero voltage switching PWM converters," in Proc. Applied Power Electronics Conf. and exposition (APEC '90), 1990, pp. 275-284

- 4. G.A.Karvelis, M.D.Manolarou, P.Manolarou, P.Malatestas, and S.N. Manias, "Analysis and design of non dissipative active clamp for forward converters," proc.inst.elect.eng, vol.148, no.5, pp.419-424. Sept.2001.

- 5. Q.Li, F.C.Lee, and M.M. Jovanovi, "Design considerations of transformer dc bias of forward converter with active-clamp reset," in proc. Applied power electronics conf. and exposition (APEC'99), 1999, pp.553-559.

- 6. H K. Ji and H.J.Kim, "Active clamp forward converter with mosfet synchronous rectification," in proc. IEEE Power Electronics Specialist's conf., 1994, pp. 895-901.

- 7. O. Garcia, J.A. Cobos, J. Uceda, and J. Sebastin, "Zero Voltage Switching in the pwm half bridge topology with complementary control and synchronous rectification," in proc. Power Electronics Specialists conf. (PESC'95), 1995, pp. 286-291.

- 8. J.Sebastin, J.A. Cobos, O. Garcia, and J. Uceda, "An overall study of the half-bridge complementary-control dc to dc converter," in proc. Power Electronics specialists conf., 1995,pp. 1229-1235.

- 9. R. Miftrakhutdinov, A.Nemchinov, V. Meleshin, and S.Fraidlin. "Modified asymmetrical ZVS half bridge DC-DC converter," in proc. Applied Power Electronics conf. and exposition (APEC'99),1999,pp.567-574.

- 10. W.Chen, P.Xu, and F.C. Lee, "The optimization of asymmetric half-bridge converter," in proc. Applied Power Electronics conf., 2001, pp.703-707.

- 11. P. Imbertson and N. Mohan, "Asymmetrical duty cycle permits zero switching loss in pwm circuits with no conduction loss penalty," IEEE trans. Power electron., vol. 29.pp.121-125, jan. 1993.

#### **About authors**

R.Madhusudhanan has obtained his B.E degree from Visveswariah Technological University in the year 2002 and M.E from Sathyabama University in the year 2004. He has teaching experience of 4 years. He is presently a research scholar at Sathyabama University. His research area is on DC-DC converters.

S.Rama Reddy has obtained AMIE in 1984 from Institution of Engineers. He has obtained his M.E degree from Anna University in the year 1987. He has done his Ph.D in the area of resonant converters in the year 1995. He has 18 years of teaching experience and 2 years of industrial experience. He is a life member of IE,IETE,SSI and SPE. His research areas are FACTS and Power Electronics Converters.