# CERTAIN INVESTIGATIONS ON HYBRID BOOST CONVERTER FOR MITIGATING POWER QUALITY ISSUES

## **R. UTHIRASAMY**\* rusamy83@gmail.com

### V. KUMAR CHINNAIYAN\*

kumarchinn@hotmail.com

### J. KARPAGAM\* jkarpagam123@gmail.com V.J.VIJAYALAKSHMI\*

vijik810@gmail.com

\*Department of Electrical and Electronics Engineering, KPR Institute of Engineering and Technology, Coimbatore, India

**Abstract:** A structure of Hybrid Boost Converter (HBC) is designed and developed for mitigating power quality issues like harmonics, voltage stress and power spectral density at the multiples of switching frequency. It consists of the boost converter, snubber modules and Hbridge inverter configuration. Compared conventional Boost Two-Level Inverter (BTLI), the proposed system employs the reduction in voltage stress, power quality issues and inverter end filter components. To obtain better quality of AC power output, Multi Carrier Sinusoidal Pulse Width Modulation (MCSPWM) technique is developed for HBC. To mitigate power quality issues, optimized firing pulses are generated using MCSPWM algorithm and the equivalent embedded C coding is fetched into micro controller. Individual voltage and current harmonics have been analyzed for various load conditions. A simulation and prototype model of the proposed HBC is developed and the system performance is validated.

*Keywords:* Hybrid converter; snubber modules; H-bridge inverter; multi carrier sinusoidal pulse width modulation.

#### 1. Introduction

In recent years, power electronics have been one of the most active areas in research and development. Different configurations of power converters have been designed to interface the renewable resources for domestic and industrial power applications. Traditional power electronic inverters are Voltage Source Inverter (VSI) and current Source Inverter (CSI). The peak DC link voltage in two-level and three-level inverter is 1.5 times higher than nominal voltage. Hence, the inverter switches are forced commutated. Soft switching techniques have been developed to reduce voltage stress and switching loss (1). In addition to this, to reduce voltage stress Multilevel Inverter (MLI) configurations are also

considered as a new breed of power converter options for high power applications (2)-(6). The efficiency and the handling of MLI systems are degraded because of more number of controlled power switches and DC sources. To reduce the switch count, source count and driver circuit utilization, certain modifications can be made in the two-level inverter and CMLI. To obtain the nominal output voltage in conventional VSI system, DC to DC converter or a magnetic component like transformer is proposed in between the DC sources and inverter circuits.

To obtain quality of power output, power electronics engineers have paid great attention to Stepped DC Link Inverter (SDCLI) as a new kind of power converter. SDCLI are emerging as the new strain of power converter options for high power applications. SDCLI can provide an efficient alternative to high power applications, providing a high quality output voltage, increasing the efficiency and robustness, and reducing the electromagnetic interference. SDCLI is not only used for achieving higher power rating but also enables the use of renewable energy sources such as PV, wind and fuel cells. The DC input voltage is boosted to the nominal voltage level by the boost chopper network (7)-(10). This results in reduction of magnetic component like transformer, number of DC sources and power switches.

The novelty of the proposed work is to encourage SDCLI instead of conventional inverter systems, thereby reducing the voltage stress, harmonics, switching loss and filter components. The significant features of the hybrid converters are reviewed in several literature papers (11)-(23).

To obtain better quality of AC power (with reduced harmonic content), MCSPWM switching strategy is developed for converter switching (24)-(30). This paper is organized as six sections are as follows; Introduction of the converters is reviewed in Section 1. Structure of HBC system is addressed in Section 2. MCSPWM switching technique is reviewed in Section 3. Performance of BTLI and proposed HBC are addressed in Section 4. Comparative analysis on BTL and HBC is described in Section 5. Section 6 concludes the paper.

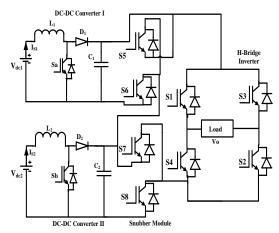

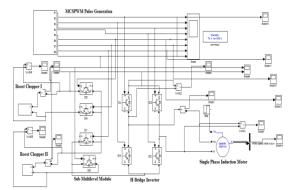

#### 2. Hybrid boost converter

The proposed structure consists of two asymmetrical DC voltage sources. The output voltage of each snubber module is always unidirectional. An H-bridge inverter is added parallel to the output of series connected snubber systems. H-bridge switches  $S_1$  and  $S_2$  are switched ON for obtaining the positive half cycle,  $S_3$  and  $S_4$  switches are turned ON for obtaining the negative half cycle of AC output voltage. Each snubber module consists of two power semiconductor switches. The equivalent structure of HBC is shown in Fig. 1.

Fig. 1. Equivalent circuit of HBC

Number of levels of HBC configuration can be expressed as;

$$N_{level} = 2(m+1)^{s} - 1 \tag{1}$$

Number of switches of HBC can be expressed as;

$$N_{Switch} = 2s + 4m + n \tag{2}$$

Where,

m - number of H-bridge inverter

s - number of DC source

n - number of boost chopper unit

To obtain AC output from two DC sources, the proposed system can be operated for 6 modes of operation.

Mode 1 and 4 operation

In mode 1 and 4 operation, the source voltage  $V_{dc1}$  is boosted to  $V_{ob1}$  by activating the boost chopper switch ( $S_a$ ). The positive and negative cycles AC output voltage is synthesized by activating the snubber switches  $S_6$  and  $S_7$  and H-bridge switches  $S_1$  and  $S_2$ ,  $S_3$  and  $S_4$  respectively.

Mode 2 and 5 operation

In mode 2 and 5 operation, the source voltage  $V_{dc2}$  is boosted to  $V_{ob2}$  by activating the boost chopper switch ( $S_b$ ). The positive and negative cycles AC output voltage is synthesized by activating the snubber switches  $S_5$  and  $S_8$ , and H-bridge switches  $S_1$  and  $S_2$ ,  $S_3$  and  $S_4$  respectively.

Mode 3 and 6 operation

In mode 3 and 6 operation, the source voltage  $V_{\text{dc1}}$  and  $V_{\text{dc2}}$  is boosted to  $V_{\text{ob1}} + V_{\text{ob2}}$  by activating the boost chopper switches ( $S_a$  and  $S_b$ ). The positive and negative cycles AC output voltage is synthesized by activating the DC link switches  $S_6$  and  $S_8$ , and H-bridge switches  $S_1$  and  $S_2$ ,  $S_3$  and  $S_4$  respectively.

At Mode 1 and 4 operations, the input voltage of H-bridge inverter can be expressed as follows;

$$\Delta V_{C1} = I_{01} * \left[ \frac{V_{01} - L_1 (I_2 - I_1)}{V_{01} * f * C_1} \right]$$

(3)

At Mode 2 and 5 operations, the input voltage of H-bridge inverter can be expressed as follows;

$$\Delta V_{C2} = I_{02} * \left[ \frac{V_{02} - L_2 (I_4 - I_3)}{V_{02} * f * C_2} \right]$$

(4)

At Mode 3 and 6 operations, the input voltage of H-bridge inverter can be expressed as follows;

$$\Delta V_{C1} + \Delta V_{C2} = I_{01} * \left[ \frac{V_{01} - L_1 (I_2 - I_1)}{V_{01} * f * C_1} \right] + I_{02} * \left[ \frac{V_{02} - L_2 (I_4 - I_3)}{V_{02} * f * C_2} \right]$$

(5)

Change in inductor currents can be expressed as follows;

$$\Delta I_{L1} = \frac{V_{dc1} * K_1}{fs * L_1} \tag{6}$$

$$\Delta I_{L2} = \frac{V_{dc2} * K_2}{f_s * L_2} \tag{7}$$

Design of  $L_1$  and  $L_2$  can be expressed as;

$$L_{1} = \frac{V_{dc1} * (V_{01} - V_{dc1})}{(I_{2} - I_{1}) * fs * V_{01}}$$

(8)

$$L_2 = \frac{V_{dc2} * (V_{02} - V_{dc2})}{(I_4 - I_3) * fs * V_{02}}$$

(9)

The voltage across the snubber module can be expressed as;

$$V_{dclink} = V_{01} + V_{02} \tag{10}$$

The voltage stress across the inverter switches can be expressed as;

$$V_{Stress} = V_{dclink \text{ min}}$$

(11)

Where,

$V_{o1}$  is the output voltage of boost chopper I  $V_{o2}$  is the output voltage of boost chopper II

## 3. Multi Carrier Sinusoidal Pulse Width Modulation Switching Technique

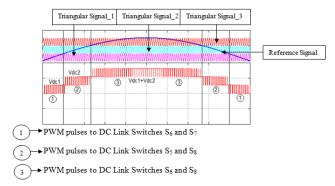

The MCSPWM switching pattern is developed to trigger the HBC switches. For developing the firing pulses, triangular signal acts as a carrier signal and sinusoidal signal acts a reference signal as shown in Fig. 2.

Each triangle signal is compared with the reference signal, when the magnitude of reference signal ( $V_{ref}$ ) is greater than triangle signals ( $V_{tri1}$ ,  $V_{tri2}$  and  $V_{tri3}$ ) the pulses  $P_1$ ,  $P_2$  and  $P_3$  are generated can be expressed as follows;

$$P_1 = V_{ref} > V_{tri1} \tag{12}$$

$$P_2 = V_{ref} > V_{tri2} \tag{13}$$

$$P_3 = V_{ref} > V_{tri3} \tag{14}$$

The total PWM switching time period of the snubber switches of  $S_5$ ,  $S_7$  and  $S_6$ ,  $S_8$  are 2.4 ms and 7.6 ms respectively. The switching frequency of snubber switches of  $S_5$ ,  $S_7$ ,  $S_6$  and  $S_8$  are 9 kHz, 7.14 kHz, 7.14 kHz and 8.33 kHz respectively. The

switching states of HBC system is summarized in Table 1.

Table 1. Switching States of HBC

| Voltag      | Level | Switching States |   |   |   |   |   |   |   |   |   |

|-------------|-------|------------------|---|---|---|---|---|---|---|---|---|

| e<br>rating | S     | S                | S | S | S | S | S | S | S | S | S |

| (V)         |       | a                | b | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| 108.4       | 1     | 1                | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 |

| 216.8       | 2     | 0                | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 |

| 325.2       | 3     | 1                | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 |

| 0           | 4     | 0                | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| -108.4      | 5     | 1                | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| -216.8      | 6     | 0                | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 |

| -325.2      | 7     | 1                | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 1 |

## 4. Performance Evaluation of BTLI and Proposed HBC Systems

## 4.1. Single Phase Boost Two-Level Inverter System

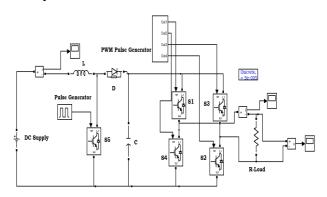

Fig. 3. Simulation model of BTLI System

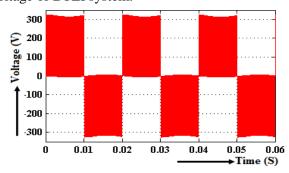

The simulation model of BTLI system is shown in Fig. 3. The entire circuit is simulated using SIMULINK tools and its performance has been investigated. Fig. 4 shows the simulated output voltage of BTLI system.

Fig. 4. Inverter Output Voltage of BTLI System

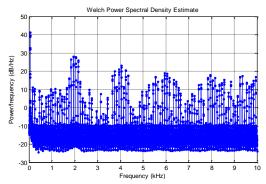

Fig. 5. Output Voltage Power Spectral Density of BTLI fed Drive Load

The power spectral density for the output voltage of BTLI fed drive load system is shown in Fig. 5. The switching frequency of two-level inverter is 2 kHz. At 2 kHz, the power spectral density for the output voltage of BTLI fed drive load is 28 dB/Hz. Similarly, at 4 kHz, the power spectral density for the output voltage of BTLI fed drive load is 24 dB/Hz. From the PSD analysis, it is understood that the density of power is maximum at the multiples of switching frequency which leads to more switching loss. Also, the analysis clearly elucidate that the two-level inverter system has high switching stress. Mathematical coding for measuring power spectral density is as follows:

signal=vlisn.signals.values; N=length(signal); Fs=2e3; // Switching frequency T=1/Fs; // Total time period t=(0:N-1)\*T; // On time period NFFT=2^nextpow2(N); // Spectrum length Y=fft(signal,NFFT)/N; f=Fs/2\*linspace(0,1,NFFT/2+2);plot(f,2\*abs(Y(1:NFFT/2+2))) // Z=Y(1:NFFT/2+3);Z1=20\*log10(Z/1e-6);plot(f,Z1(1:NFFT/2+3))%plot(f,Y (1:NFFT/2+1)) title('Single Sided Amplitude Spectrum of vlisn') xlabel('Frequency in Hz') ylabel('|Signal(f)|')

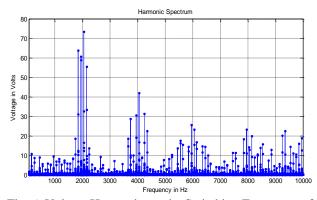

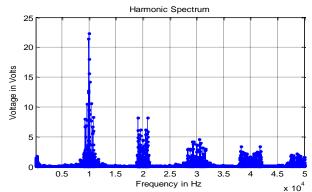

Voltage harmonics at the multiples of switching frequency has been examined using FFT algorithm. The voltage harmonics at the switching frequency of BTLI fed drive load systems are shown in Fig. 6. At 2 kHz, the magnitude of voltage harmonics of BTLI fed drive load is 72 V. Similarly, at 4 kHz, the magnitude of voltage harmonics of BTLI fed drive load is 42 V. From the harmonic analysis, it is

understood that the BTLI has high power loss at the multiples of switching frequency.

Fig. 6. Voltage Harmonics at the Switching Frequency of BTLI fed Drive Load

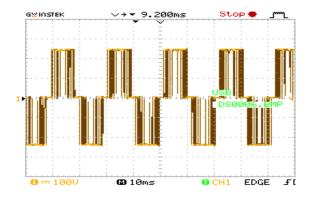

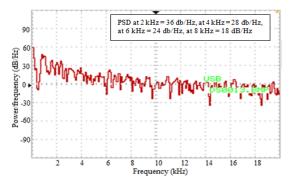

Fig. 7 shows the experimented output voltage of BTLI fed drive system. The obtained result has the voltage magnitude and frequency of 240 V, 50 Hz respectively. The power spectral density for the experimented output voltage of BTLI fed drive load system is shown in Fig. 8. At 2 kHz, the power spectral density for the output voltage of BTLI fed drive load is 36 dB/Hz, Similarly, at 4 kHz, the power spectral density for the output voltage of BTLI fed drive load is 28 dB/Hz.

Fig. 7. Experimented Inverter Output Voltage of BTLI fed Drive Load

Fig. 8. Experimented Output Voltage Power Spectral Density of BTLI fed Drive Load

# **4.2.** Single Phase Boost Hybrid Converter System-Simulation Model and Analysis

The simulation model of HBC fed AC load system is shown in Fig. 9. The entire circuit is simulated using SIMULINK tools and their performance is evaluated. Two asymmetrical DC sources (38 V and 76 V) are connected with boost chopper unit I and

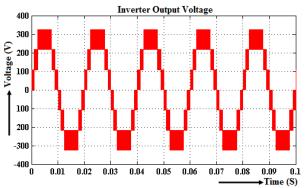

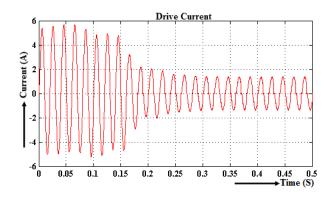

boost chopper unit II. The output of boost chopper units (110 V and 215 V) are connected with respective DC link modules. The outputs of DC link modules are synchronized with H-bridge inverter system. The output voltage and load current of HBC fed drive load system is shown in Fig. 10 and Fig. 11 respectively.

Fig. 9. Simulation model of HBC fed AC load system

Fig. 10. Inverter Output Voltage of BCDCLHBI fed Drive Load System

Fig. 11. Load Current of HBC

Fig. 12. Power Spectral Density of Output Voltage of HBC fed Drive Load

| Converter<br>System | Switching<br>Frequency<br>(kHz) | Power<br>Density<br>(dB/Hz) |

|---------------------|---------------------------------|-----------------------------|

| ъ . п               | 2                               | 28                          |

| Boost Two-          | 4                               | 24                          |

| Level Inverter      | 6                               | 19                          |

Table 2. PSD analysis of BTLI system

| Converter<br>System | Switching<br>Frequency<br>(kHz) | Power<br>Density<br>(dB/Hz) |

|---------------------|---------------------------------|-----------------------------|

| D                   | 10                              | 18                          |

| Boost Hybrid        | 20                              | 8                           |

| Converter           | 30                              | 4                           |

Table 3. PSD analysis of HBC system

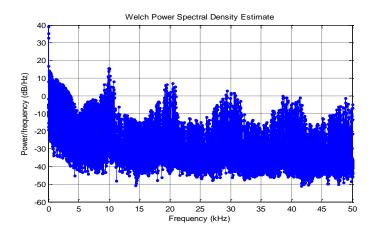

The power spectral density for output voltage of HBC fed drive load system is shown in Fig. 12. The switching frequency of proposed HBC is 10 kHz. At 10 kHz, the power spectral density for the output voltage of HBC fed drive load is 18 dB/Hz. Similarly, at 20 kHz, the power spectral density is 8 dB/Hz. From the PSD analysis, it is understood that the density of power at the multiples of switching frequency in the HBC system gets reduced compared to BTLI system. Also, the analysis clearly elucidate that the HBC system has reduced switching stress compared to BTLI system. The PSD analysis of BTLI and HBC systems are tabulated in Table 2 and Table 3 respectively.

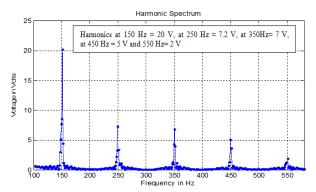

Fig. 13. Multiples of Switching Harmonics of Output Voltage of HBC

The voltage harmonics at the multiples of switching frequency of HBC is shown in Fig. 13. At 10 kHz, the magnitude of voltage harmonics of HBC drive load is 23 V. Similarly, at 20 kHz, the magnitude of voltage harmonics is 8 V. From the harmonic analysis, it is understood that the proposed converter has reduced power loss, harmonics and reduced switching stress at the multiples of switching frequency. The individual harmonics analysis of output voltage and load current of the proposed converter is shown in Fig. 14 and Fig. 15 respectively.

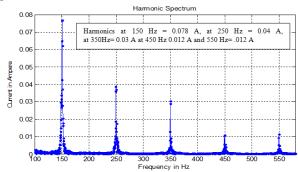

Fig. 14. Individual Harmonics of HBC fed Drive Load

Fig. 15. Individual Current Harmonics of HBC fed Drive Load

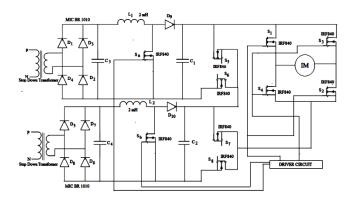

# 4.3. Single Phase Boost Hybrid Converter System-Experimental Model

The prototype model of HBC consists of power supply unit, controller unit, driver unit and converter unit. The microcontroller unit provides the control signals to the MOSFET driver circuit. The snubber module and H-bridge inverter systems are designed using IRF840 power MOSFET. The floating channel can be used to drive an N-channel enhancement type power MOSFET in the high side configuration which operates up to 500 or 600 V. In the prototype model, MCSPWM based seven-level staircase AC output voltage is synthesized. The equivalent circuit of HBC system is shown in Fig. 16. Driver unit consists of ICL7667 integrated circuits and its biasing components. For isolating the low voltage operated control circuit from the high power circuit an opto-coupler is used. Isolation process is achieved by 6N135 integrated circuits.

Fig. 16. Hardware Circuit of Hybrid Boost Converter

## **4.4.** Single Phase Boost Hybrid Converter System- Soft Switching Capability

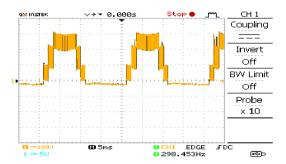

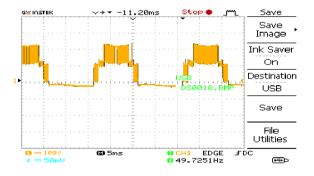

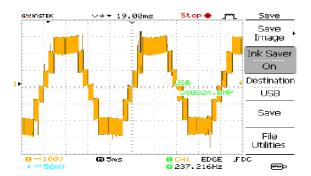

The voltage across the H-bridge inverter switches are shown in Fig. 17 and Fig. 18. From the obtained waveforms, it is understood that the H-bridge inverter switches are getting triggered at every zero crossing points of DC link voltage. Hence, the voltage stress across the H-bridge inverter switches is getting reduced. Fig. 19 shows the output voltage of HBC system. Harmonic analysis also made for the output voltage and load current of the proposed HBC using ALM make ALM 10 PQ analyzer.

Fig. 17. Soft Switched Output Voltage of Inverter Switch S<sub>3</sub> and S<sub>4</sub>

Fig. 18. Soft Switched Output Voltage of Inverter Switch  $S_1$  and  $S_2$

Fig. 19. Output Voltage of HBC

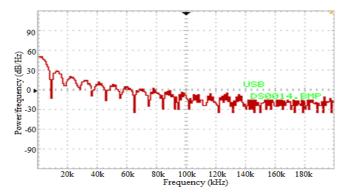

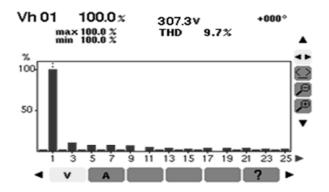

The power spectral density of the experimented output voltage of HBC fed drive load system is shown in Fig. 20. At 20 kHz, the power spectral density for the output voltage of BTLI fed drive load is 15 dB/Hz. Similarly, at 20 kHz, the power spectral density for the output voltage of BTLI fed drive load is 5 dB/Hz. From the spectrum, it is inferred that the proposed system has reduced lower order harmonics. The experimental output voltage THD spectrum of the proposed system is also shown in Fig. 21. From the spectrum, it is clearly observed that the output voltage THD is 9.7%. The simulated results are validated with the experimented results. The proposed system is recommended for solar powered UPS system. From the harmonics analysis it is inferred that magnitude of lower order harmonics are low and hence the inverter end filter component is eliminated in the proposed HBC system. This adds one of the remarkable advantages of the proposed converter.

### **Design Procedure**

$$\Delta I_{L1} = (V_{dcl} * K_1) / f_s * L_1 \text{ (Based on } V_{dc1})$$

= (36\*0.67)/ 10\*10<sup>3</sup>\*2<sup>e-3</sup>

= 1.2 A

$$\Delta I_{L1} = (V_{dcl} * K_1) / f_s * L_1 \text{ (Based on } V_{dc2})$$

= (76\*0.67)/ 10\*10<sup>3</sup>\*2<sup>e-3</sup>

= 1.2 A

### Design of Inductor L<sub>1</sub>

$$L_{1} = \frac{V_{dc1}^{*}(V_{ob1}^{-}V_{dc1}^{-})}{\Delta I L 1^{*} f s^{*}V_{ob1}}$$

$$= \frac{36.3^{*}(52.6 - 36.3)}{(0.56^{*}1000^{*}52.6)} = L_{1} = 2.00872 \text{ mH}$$

Fig. 20. Experimented Output Voltage Power Spectral Density of HBC

Fig. 21. Output Voltage THD Spectrum of HBC

### 5. Comparative Analysis

Performance analysis is made between BTL and HBC with respect to the parameters such as; individual harmonics, Total Harmonic Distortion (THD), PSD, soft switching operating area, voltage stress and inverter end filter requirements. From the analysis, it is inferred that the proposed HBC has reduced switching loss of 42.26 % and has wide soft switching area with reduced voltage stress, inverter end filter components.

### 6. Conclusion

Certain power quality investigations such as harmonics analysis, PSD analysis and THD analysis were conducted on both BTL and HBC and it is inferred that the proposed HBC systems shows remarkable output results. Simulation and prototype models of HBC systems have been implemented and various parameters are analyzed. Soft switching nature, minimized PSD at the multiples of switching frequency, reduced voltage and current THD conclude that the proposed converter is considered as appropriate power converters for single phase solar powered UPS systems.

#### References

- 1. Abu-Rub, H, Holtz, J, Rodriguez, J & Baoming, G, Medium voltage multilevel converters-state of the art, challenges and requirements in industrial applications, *IEEE Trans. Ind. Electron.* 57 (2010) 2997-3004.

- Kumar Chinnaiyan, V, Jovitha Jerome, Karpagam, J, An experimental investigation on multilevel inverter for solar energy applications," *International Journal of Electrical Power and Energy Systems*, 47 (2013) 157-167.

- 3. Kouro, S, Malinowski, M, Gopakumar, K, Pou, J, Franquelo, LG, Wu, B, Rodriguez, J, Perez, MA & Leon, JI, Recent advances and industrial applications of multilevel converters, *IEEE Trans. Ind. Electron.* 57 (2010) 2553-25803.

- IlhamiColak, ErsanKabalci, RamazanBayindir, Review of multilevel voltage source inverter topologies and control schemes, *International Journal of Energy Conversion Management*, 9 (2010) 1-15.

- M. R. Banaei, H. Khounjahan, E. Salary, Implementation of Multi Transformer Cell Inverter with Reduced Switches in Last Cell, *Journal of Circuits, Systems and Computers*, 22 (2013).

- Walker, GR & Sernia, PC, Cascaded DC–DC converter connection of photovoltaic modules, *IEEE Trans. Power Electron.* 19 (2004) 1130-1139.

- 7. Yuan, X & Barbi, I, Soft-switched three-level capacitor clamping inverter with clamping voltage stabilization, *IEEE Trans. Ind. Applicat.* 35 (2000) 1165-1173.

- 8. B.R. Lin, ZVS Converter with Full-Bridge and Half-Bridge Circuits: Analysis, Design and Implementation, *Journal of Circuits, Systems and Computers*, 26 (2017)

- 9. MiaosenShen, Fang ZhengPeng, Leon M. Tolbert, Multilevel DC–DC power conversion system with multiple DC sources, *IEEE Trans. Power Electron.* 23 (2008) 420–426.

- Uthirasamy, R., Ragupathy, U. S., Kumar Chinnaiyan, V., Megha, C, Experimentation of boost chopper interfaced cascaded multilevel inverter topology for photo voltaic applications, *International Review of Electrical Engineering*, 9 (2014)16-25.

- 11. Ebrahimi, J, Babaei, E & Gharehpetian, GB, A New Multilevel Converter Topology With Reduced Number of Power Electronic Components, *IEEE Trans. Ind. Electron.* 59 (2012) 655-667.

- Ramasami Uthirasamy, Uthandipalayam Subramaniyam Ragupathy, Venkatachalam Kumar Chinnaiyan, Structure of boost DC-link cascaded multilevel inverter for uninterrupted

- power supply applications, *IET Power Electronics*, Online 7(2015), 1-12.

- 13. E. Babaei, A cascade multilevel converter topology with reduced number of switches, *IEEE Trans. Power Electron.* 23 (2008) 2657-2664.

- 14. Kangarlu, MF & Babaei, E, A generalized cascaded multilevel inverter using series connection of sub-multilevel inverters," *IEEE Trans. Power Electron.* 28 (2013) 625-636.

- 15. Mohammad Reza Jannati Oskuee, Sahar Khalilnasab, Sajad Najafi Ravadanegh, Gevork B. Gharehpetian, Reduction of Circuit Devices in Developed Symmetrical/Asymmetrical Multilevel Converters, *Journal of Circuits, Systems and Computers*, 25 (2016).

- Najafi, E & Mohamed Yatim, AH,Design and implementation of a new multilevel inverter topology, *IEEE Trans. Ind. Electron.* 59 (2012) 4148-4154.

- 17. M. R. Banaei, E. Salary, Analysis of a generalized symmetrical multilevel inverter, *Journal of Circuits, Systems and Computers*, 20 (2011) 299-311.

- Ali Ajami, Mohammad Reza JannatiOskuee, Mahdi ToopchiKhosroshahi, Ataollah Mokhberdoran, Cascade-multi-cell multilevel converter with reduced number of switches, *IET Power Electronics*, 3 (2014) 552-558.

- 19. Rohollah Abdollahi, Design and Experimental Verification of 20-Pulse AC–DC Converter for Retrofit Applications and Harmonic Mitigation, *Journal of Circuits, Systems and Computers*, 26 (2017).

- AmmarMasaoud, Hew Wooi Ping, SaadMekhilef, AyoubTaallah, Novel configuration for multilevel DC-link three-phase five-level inverter, *IET Power Electronics*, 12 (2014) 3052-3061.

- RasoulShalchiAlishah, DaryooshNazarpour, SeyyedHosseinHosseini, MehranSabahi, New hybrid structure for multilevel inverter with fewer number of components for high-voltage levels, *IET Power Electronics*, 1 (2014) 96-104.

- 22. MohammadrezaMiranbeigi, HosseinIman-Eini, Mohsen Asoodar, A new switching strategy for transformer-less back-to-back cascaded H-bridge multilevel converter, *IET Power Electronics*, 7 (2014) 1868-1877.

- 23. MiroMilanovic, Franc Mihalic, DragoDolinar, Component minimized topology of DC to three-phase inverter, *Journal of Circuits, Systems and Computers*, 13 (2004) 863-875.

- 24. Keith A. Corzine, Mike W. Wielebski, Fang Z. Peng, Jin Wang, Control of cascaded multilevel inverters, *IEEE Trans. Power Electron.* 19 (2004) 732-738.

- Leon M. Tolbert, Thomas G. Habetler, Novel multilevel inverter carrier-based PWM method, *IEEE Trans. Ind. Applicat.* 35 (1999) 1098-1107.

- A. S. Aneesh Mohamed, AnishGopinath, M. R. Baiju, A simple space vector PWM generation scheme for any general n-level inverter, *IEEE Trans. on Ind. Electron.* 56 (2009) 1649-1656.

- Zhi-G. Lu, Li-L. Zhao, Wan-P. Zhu, Chun-J. Wu, Yu-S. Qin, Research on cascaded three-phase-bridge multilevel converter based on CPS-PWM, *IET Power Electronics*, 6 (2013) 1088-1099.

- Charles I. Odeh, Vincent N. Agu, NentaweGoshwe, Cascaded three-phase pulsewidth modulated switched voltage source inverter, *IET Power Electronics*, 7 (2014) 1925-1983.

- Jose Rodriguez, Luis Moran, Pablo Correa, Cesar Silva, A vector control technique for medium-voltage multilevel inverters, *IEEE Trans. Ind. Electron.* 49 (2002) 882-888.

- J. I. Leon, S. Vazquez, S. Kouro, L. G. Franquelo, J. M. Carrasco, J. Rodriguez, Unidimensional modulation technique for cascaded multilevel converters, *IEEE Trans. Ind. Electron.* 56 (2009) 2981-2986.